# Frequency-Modulated Continuous-Wave Radar

Group 16

Casey Sanchez (EE)

Fahim Ahmed (EE)

Mikayla Peña (EE)

Sebastian Peralta (EE)

Sponsor: Dr. Xun Gong, UCF Professor

December 6, 2022

# **Table of Contents**

| 1. | Executive       | Summary       |                                   | 1  |  |

|----|-----------------|---------------|-----------------------------------|----|--|

| 2. | Project De      | scription     |                                   | 1  |  |

|    | 2.1. Motiv      | ation         |                                   | 1  |  |

|    | 2.2. Goals      |               |                                   |    |  |

|    | 2.3. Objectives |               |                                   |    |  |

|    | 2.4. Requ       | irement Spe   | cifications                       | 6  |  |

|    | 2.4.1.          | Desired Sys   | stem Qualities                    | 6  |  |

|    |                 | 2.4.1.1.      | Accuracy Requirements             | 6  |  |

|    |                 | 2.4.1.2.      | Operating Distance Requirement    | 7  |  |

|    |                 | 2.4.1.3.      | System Runtime Requirement        | 7  |  |

|    |                 | 2.4.1.4.      | Transmitted Frequency Requirement | 8  |  |

|    |                 | 2.4.1.5.      | Module Size Requirements          | 8  |  |

|    |                 | 2.4.1.6.      | System Cost Requirement           | 8  |  |

|    | 2.4.2.          | Requiremen    | nts Summary                       | 8  |  |

|    | 2.4.3.          | House of Q    | uality                            | 9  |  |

| 3. | Project Re      | search        |                                   | 10 |  |

|    | 3.1. Rada       | r Backgroun   | d Theory                          | 10 |  |

|    | 3.1.1.          | Radar Tran    | smission Theory                   | 10 |  |

|    | 3.1.2.          | Microwave     | Theory                            | 12 |  |

|    | 3.1.3.          | Antennas a    | nd Electromagnetics               | 16 |  |

|    | 3.2. Simila     | ar Products . |                                   | 19 |  |

|    |                 |               | Radar System                      |    |  |

|    | 3.2.2.          | Police Rada   | ar Systems                        | 19 |  |

|    | 3.2.3.          | Automatic [   | Doors                             | 19 |  |

|    | 3.3. Relev      | ant Technol   | ogies                             | 20 |  |

|    | 3.3.1.          | Remote Se     | nsing                             | 20 |  |

|    |                 |               | oler Signal Processing            |    |  |

|    | 3.3.3.          |               | r Architectures                   |    |  |

|    |                 | 3.3.3.1.      | Time-Domain Duplexing Model       | 21 |  |

|    |                 | 3.3.3.2.      | Frequency-Domain Duplexing Model  | 22 |  |

|    |                 | 3.3.3.3.      | Direct Conversion Receiver        | 22 |  |

|    |                 | 3.3.3.4.      | Heterodyne Receiver               |    |  |

|    | 3.4. Strate     | egic Compor   | nents and Part Selections         | 24 |  |

|    | 3.4.1.          |               | Processing Components             |    |  |

|    | 3.4.2.          |               | Description                       |    |  |

|    |                 |               |                                   |    |  |

|    | 3.4.4.          |               |                                   |    |  |

|    | 3.4.5.          | Power Amp     | olifier                           | 28 |  |

|    |                 |               |                                   |    |  |

|    | 3.4.7.          | Low Noise     | Amplifiers                        | 30 |  |

|    |                 | _             | Digital Converters                |    |  |

|    |                 |               | oller                             |    |  |

|    |                 |               | ll Amplifiers                     |    |  |

|    |                 |               | n Block Diagram                   |    |  |

| 4. | Project Constraints                                           | 36 |

|----|---------------------------------------------------------------|----|

|    | 4.1. Standards                                                | 36 |

|    | 4.1.1. Hardware Standards                                     | 36 |

|    | 4.1.1.1. IEC 60086-1 Primary Batteries - General              | 36 |

|    | 4.1.1.2. ANSI C18.1M – Portable Primary Cells                 | 37 |

|    | 4.1.1.3. IEC 61169-15 – Radio Frequency Connectors (SMA)      | 37 |

|    | 4.1.2. Software Standards                                     |    |

|    | 4.1.2.1. ISO/IEC 14882:2020(E) - Programming Language C++     | 38 |

|    | 4.1.2.2. ISO/IEC 9899:2018 – Programming Language C           | 39 |

|    | 4.1.2.3. Arduino Language Standard API                        | 39 |

|    | 4.1.2.4. Ripple Radar API Standard                            | 39 |

|    | 4.1.3. Hardware/Software Hybrid Standards                     | 39 |

|    | 4.1.3.1. IEC 62680-2-1 – USB Specification                    | 39 |

|    | 4.1.3.2. SCPI-99 – Std. Commands for Programmable Instruments | 40 |

|    | 4.1.3.3. VISA - Virtual Instrument Software Architecture      | 40 |

|    | 4.2. Constraints                                              |    |

|    | 4.2.1. Federal Communication Commission                       | 41 |

|    | 4.2.2. Time Constraints                                       |    |

|    | 4.2.3. Economic Constraints                                   |    |

|    | 4.2.4. Health and Safety Constraints                          | 43 |

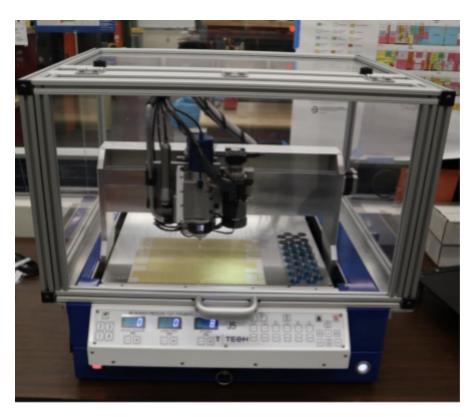

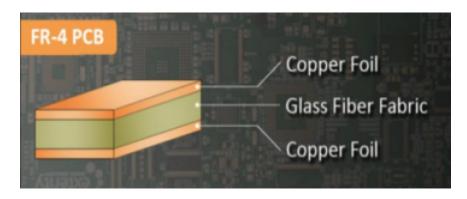

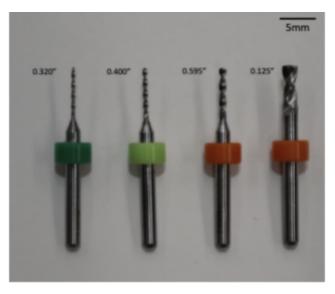

|    | 4.2.5. Manufacturability Constraints                          | 44 |

| 5. | Hardware Design                                               | 44 |

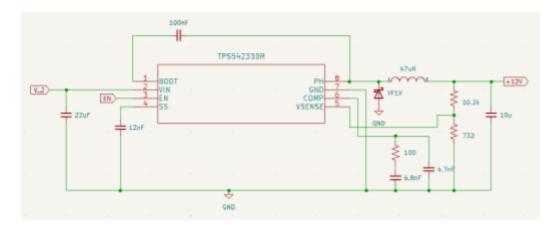

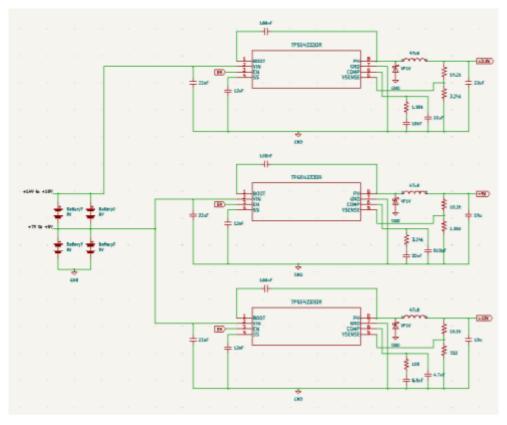

|    | 5.1. Power Supply Design                                      | 45 |

|    | 5.1.1. Battery Selection and Configuration                    |    |

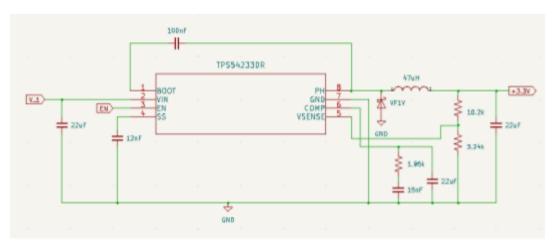

|    | 5.1.2. +3.3V Power Supply                                     |    |

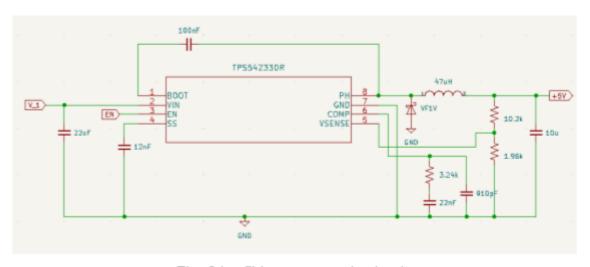

|    | 5.1.3. +5V Power Supply                                       | 48 |

|    | 5.1.4. +12V Power Supply                                      | 48 |

|    | 5.1.5. Complete Power Supply Circuit                          |    |

|    | 5.1.6. Power Enable Functionality                             |    |

|    | 5.2. Modulator Circuit and Oscillator                         |    |

|    | 5.3. RF Subsystem Design                                      |    |

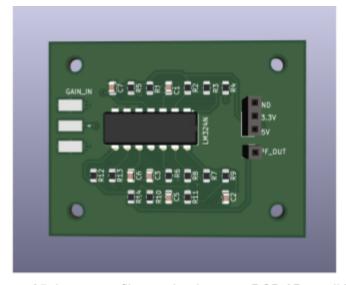

|    | 5.4. Gain Stage Design                                        |    |

|    | 5.5. Low Pass Filter Design                                   |    |

|    | 5.6. Analog-to-Digital Converter Circuit Design               |    |

| _  | 5.7. PCB Vendor and Assembly                                  |    |

| 6. | Software Design                                               |    |

|    | 6.1. Real-Time Processing                                     |    |

|    | 6.2. Ripple Interface                                         |    |

|    | 6.3. Module-to-Host Data Transmission                         |    |

|    | 6.4. Ranging and Velocity Computation                         |    |

| _  | 6.5. Graphical User Interface                                 |    |

| 7. | Project Prototype Construction                                |    |

|    | 7.1. PCB Design Standardization                               |    |

|    | 7.2. PCB Prototyping                                          |    |

|    | 7.3. Power Supply PCB                                         |    |

|    | 7.4. Modulator PCB                                            | 89 |

| 7.5. Gain Stage and Low Pass Filter PCB            | 89  |

|----------------------------------------------------|-----|

| 7.6. ADC PCB                                       |     |

| 8. Project Prototype Testing Plan                  |     |

| 8.1. Required Equipment                            |     |

| 8.1.1. Multimeter                                  |     |

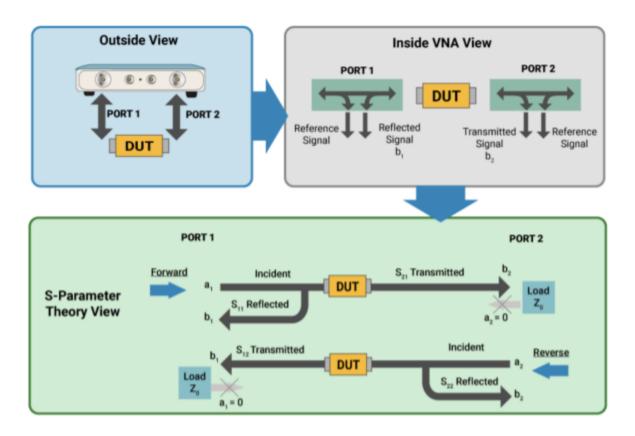

| 8.1.2. Network Analyzer                            | 92  |

| 8.1.3. DC Power Supply                             | 93  |

| 8.1.4. Oscilloscope                                | 93  |

| 8.1.5. Function Generator                          |     |

| 8.2. Hardware Specific Testing                     | 94  |

| 8.2.1. Antenna Test                                |     |

| 8.2.1.1. S-Parameters                              | 96  |

| 8.2.1.2. Impedance Testing                         | 99  |

| 8.2.1.3. The Smith Chart                           | 100 |

| 8.2.1.4. Radiation Pattern & Antenna Gain          | 101 |

| 8.2.2. Power Supply Test                           | 101 |

| 8.2.3. Modulator Test                              | 102 |

| 8.2.4. Gain Stage Test                             | 105 |

| 8.2.5. Low Pass Filter Test                        | 108 |

| 8.3. Software Specific Testing                     | 110 |

| 8.3.1. Ripple API Test                             | 110 |

| 8.3.2. USB Interface Test                          | 110 |

| 9. Administrative Material                         | 110 |

| 9.1. Project Milestones                            | 110 |

| 9.1.1. Progress Recap                              | 110 |

| 9.1.2. Design Verification and Part Acquisition    |     |

| 9.1.3. Project Construction and System Integration | 112 |

| 9.1.4. Prototype Demonstration                     | 113 |

| 9.1.5. Documentation and Further Development       |     |

| 9.2. Budget and Finance Discussion                 | 114 |

| 10. Conclusion                                     |     |

| 11. Appendices                                     | 121 |

| 11.1. References                                   | 121 |

# 1.0 Executive Summary

Radar systems have become a prevalent technology in modern times. Due to their versatility, they can be found in a variety of applications, from tracking global weather patterns to mapping terrain. Parameters such as frequency, antenna size, antenna number, power level and mobility all play a part in determining a particular radar's capabilities and what kind of information can be extracted from its received signal. Although large, high-power radar systems have their place, particularly in the defense and aerospace industries, small-scale radar are oftentimes better suited for everyday consumer use. These systems can be used for applications where high power and large range are not necessary, but relatively small dimensions, ease of use, low cost, and direct access to the necessary information is a priority.

One piece of information that radar systems are often used to find is the velocity of objects in the radar's field of view; this system is often referred to as a Doppler radar given that it uses the Doppler effect to calculate the velocities. This velocity information can be used simply to analyze an environment, or it could be used to control an additional subsystem. Although radar data could be utilized post-collection, a more versatile system would have software that could process the collected data in real-time. Our team's project is to design such a system. We plan to build a portable, frequency-modulated continuous-wave (FMCW) radar module and implement a user-friendly application programming interface to accompany it. The API will allow the user to easily extract different information from the raw radar data in real time.

The system will be divided into three parts: the radar module itself (purely hardware), the API (purely software) and the USB interface between them (a combination of hardware and software). A signal of a certain frequency will be transmitted from the radar module, and that signal will bounce off objects in the environment and return to the radar receive antenna. The signal is then filtered and amplified in hardware and sent through the USB interface to the host computer. The host computer will then use our API to extract the desired information from the raw data.

One of the main concepts of our project is that it is a multi-purpose consumer product. The radar module and accompanying software can be used by a consumer for a variety of applications, and any particular use of the system does not define the limits of the system's capabilities. In order to demonstrate just one application of the system, our team will position the radar module beside Pegasus Drive on UCF's main campus. We will use our system to track, in real-time, the maximum velocity of vehicles on that street.

# 2.0 Project Description

#### 2.1 Motivation

Radar system design is highly diverse from a technical perspective, spanning topics from wireless communication to programming digital user interfaces. A project such as

our radar system therefore involves knowledge of several electrical engineering subdisciplines. Design of the FMCW radar itself requires knowledge of microwave signal propagation and radio frequency signal processing. The USB interface consists of an analog to digital converter and microcontroller, which requires knowledge of embedded systems. And implementing the API involves programming and digital signal processing. This means that each of our team members will be able to demonstrate technical ability in the area related to their academic subfield. Additionally, due to signals traveling through the subsystems sequentially, team members will also need to have a basic understanding of subsystems interacting with their own. This affords an excellent opportunity for the team to expand our knowledge beyond the subfield-specific courses we have chosen on our academic track. The diversity in our system's technical requirements and the subsystem interconnectivity presents a challenge that our team is ready and willing to take on.

Another motivation our team has for completing this project is the wide range of possibilities for application of our system. We will only be demonstrating one application of our system for academic purposes, but in reality, our system could be used for many other things. The main advantage of our system is that the radar module is portable, meaning it is ideal for aiming at different targets while maintaining its wide field of view. Tracking the speed of vehicles, measuring terrain height, and monitoring activity in parking garages are just a few examples of how our system could be used.

Lastly, as aforementioned, one of our main focuses is creating a consumer product. Given our constraints, our end product for academic purposes will likely leave much room for future improvement from a marketing standpoint. Consumer needs would ultimately drive further development of the system design, both on the hardware and software side. The software capability could be expanded to extract additional parameters from the radar data or potentially present the information pictorially rather than numerically. The hardware could be modified to allow for the radar frequency or power to be set by the user, according to what is required of the specific application. The size and aesthetics of the system could also be improved. Completing our project is just the first step to creating a highly successful, marketable product.

#### 2.2 Goals

There are three goals for the FMCW radar project. The primary goal aligns with our system's minimum expected level of functionality, and it is to measure the velocity of vehicles on Pegasus Drive on UCF's main campus. Successfully completing this goal will demonstrate that the radar module and API are capable of detecting movement in a dynamic environment. Pegasus Drive is a convenient location for the demonstration because vehicles often accelerate and decelerate in a short span of time due to foot traffic across the drive. This will allow our team to verify that our system can accurately detect velocity even with nonzero acceleration present. For the demonstration, the radar and host CPU will be positioned beside Pegasus Drive, pointed toward oncoming traffic. Either direction of traffic would do, but ideally the radar should be positioned in a way as to minimize interfering readings from background movement. During the demonstration,

the radar will remain on, and at a minimum, the API should output the maximum detected velocity at any given moment. For instance, if a vehicle turns the corner slowly, speeds up, and then comes to a stop, the real-time readings output by the software should begin low, increase and then decrease to 0, with all readings remaining within the allowed margin of error. As an extension of this demonstration, the system can be taken to alternative locations to test for higher velocity readings (Gemini Boulevard would be a good alternative).

The second goal for our project is to demonstrate the ranging functionality of our radar. This is designated as a stretch goal because achieving it will require additional work on the software side of the design. It will be worked toward if the projected completion date of the primary goal is well before the scheduled deadline. For the ranging demonstration, the radar should be connected to the host computer in a way that allows the module to be pointed in different directions. To verify that the system can accurately detect range, the radar should be pointed at stationary, relatively large objects that span a range of distances away. A convenient place to perform the demonstration would be in the UCF arboretum, where there are many large trees and very few moving objects to interfere with the readings. The API output should update in real-time to show the minimum distance detected by the radar.

The final goal for our project, and the second stretch goal, is to use the data output from our API as the input to a feedforward control system. The output of the control system could be used as an alternative way to visualize the velocity or ranging data being collected from the radar. A relatively simple example would be to feed the velocity output of the API to a microcontroller, which then controls a series of LEDs. The maximum velocity detected by the radar could linearly relate to the speed at which the LEDs blink, or perhaps the velocities could map to a color spectrum, where blue corresponds to slow speeds and red to high speeds. Whatever implementation is chosen, this final goal will require the most design work for both the hardware and software. It will be attempted after goals one and two are completed, and if the schedule allows for it.

One important characteristic of these three technical goals is that they all operate in real time. The real-time signal processing is entirely dependent on the success of the USB interface and data retrieval aspect of the software, which is the most complex part of the project design. In addition to defining stretch goals, our team has also defined a "bare minimum" goal. This bare minimum goal eliminates the need for real-time data processing. It simply requires that one (or more) of the aforementioned goals be achieved without the need for the information to be processed in real-time. For instance, rather than the API output velocity readings from cars in real-time, the received radar signal can be recorded for a certain length of time, then loaded into the API for post-processing. A corresponding visual of what would have been seen during real-time operation would be the acceptable output of the API for this bare minimum goal.

In addition to the team's technical goals, there are also project management goals the team will strive to achieve. The first is closely related to the technical goals, and this is

keeping an accurate record of the project design iterations. Every concrete design change the team makes from start to finish should be well documented. This includes modifications to existing designs from external sources and any changes made from our original designs for each subsystem. Changes should be accompanied by a reason the change was made. The design documentation should be updated on a monthly basis.

A second project management goal is to perform and document the results of our final demonstration. Regardless of which technical goals are ultimately achieved or which design iteration of the project subsystems is used, the results of the system demonstration need to be well-documented. In general, the project results should include an externally measured input parameter (such as the actual distance to an object), the radar measured parameter (being the output of our software), the calculated error and the time delay (if the demonstration is performed in real-time). These four parameters should be measured and recorded for at least four targets per technical goal. Documentation of the final demonstration is important because it shows the proven capability achieved by the system at its last design iteration. The more technical goals we can achieve, the better, because more demonstrations will show the full extent of the final system's capabilities.

Lastly, our team strives to meet on a regular basis and keep to our project schedule. The best way to ensure the team meets its deadlines, both those from the Senior Design course and those created by our team, is to track progress towards objectives at least twice a week. Our team will meet with this frequency and record what progress each team member has made toward their individually assigned goals since last meeting. This will make it clear whether the team is making sufficient progress towards meeting our deadlines.

# 2.3 Objectives

In order to achieve our goals, steps must be taken to design and complete each of the subsystems in the project. The three subsystems are the radar module, the USB interface, and the API. Each of these subsystems varies in the amount of effort needed to design and construct it, and the effort generally increases as we aim to achieve each of the successive goals outlined in the previous section. We will begin with a discussion of the first subsystem, the radar module.

Our radar module is centered around the MIT Lincoln Laboratory laptop-based radar, which anyone can build as they work through the corresponding MIT OpenCourseWare material. The details of that project will be discussed in further detail in Section 3.1 "Similar Products." There are two categories in which the components for the radar can be placed: those that operate at higher, microwave frequencies, and those that operate at lower, radio frequencies. There are also mixers that convert from one frequency to another, but for the purposes of this discussion, the mixers will be placed in the microwave frequency category.

Dr. Xun Gong, professor at the University of Central Florida and the primary advisor for our project, has provided our group with a partially built version of the MIT radar for us to start with. The part of the radar he provided includes all the high-frequency components; they are assembled and fully functional. What is left to be completed is the low-frequency circuits, which are the low-pass filter, gain stage, and modulator. MIT OpenCourseWare provides schematics for these circuits, but the course is dated and details regarding the design of the circuits is limited. In order to complete the radar, our team will need to update the designs for each circuit and test them to verify proper operation. Once the circuits have been tested, the team can design printed circuit boards for use in the final module prototype. Work regarding completion of the radar module constitutes our team's first objective.

The second objective is to design an operational USB interface. A variety of interfaces can be used to communicate between the radar module and the host computer, including wireless communication or the audio interface already used in MIT's project design. Our team has decided that a USB interface would be a fair compromise between feasibility and ease of use. The input of the circuit is the analog output of the radar module. The output of the interface is a digitized version of the radar output, sent through USB2. The interface should transmit the digitized signal quickly and with minimal error introduced.

The third objective is to design a functional and easy-to-use API. There is much room for flexibility in the implementation of this API. Further details will be discussed in a later section, but the most beneficial characteristic of the API is that it will be aligned with radar signal processing standards. This is not a necessity, but using a standard will ensure that the functions and architectures are easily understood by certain end users who wish to slightly modify the functionality of the system. For the purposes of our team's project, the code developed should not only be able to extract the necessary information from the radar module signal but should also be somewhat adaptable. Certain parts of the final code may ultimately go unused in our demonstrations, but they will be available for later use.

Because the three goals for the project each have their own requirements for the API, depending on which goals the team has the resources to aim for, the built-in capabilities of the API will be changed or added upon as needed. For our primary goal, the only necessary capability of the API is that it takes in a digitized received radar signal and outputs the maximum instantaneous velocity detected in real time. For our second goal, the API must also be able to extract range information, and for the final goal, the API must use a standard communication protocol to output either velocity or ranging information to an external device such as a microcontroller.

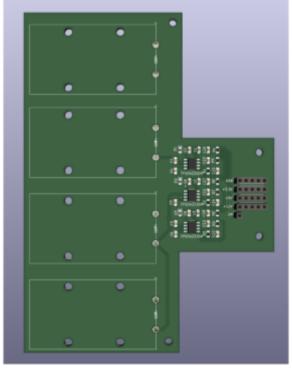

The fourth objective is to design the PCBs for the project. Two things will be taken into consideration to design the PCBs. The first is testing. The more components that are placed on a single PCB, the harder it is to troubleshoot issues. The circuitry for the project will therefore be broken up into multiple PCBs to facilitate the testing process. The second consideration is the size and shape of the PCBs. Although the overall size

of the radar module will be largely dictated by the size of the antennas, which have already been provided by Dr. Gong, it is still important to ensure the shape of the PCB makes it easy to install on the final system. Additionally, the components to be soldered onto the PCB should be large enough for easy assembly, but not so large as to make the entire PCB footprint unnecessarily large.

The fifth and sixth objectives are to acquire the necessary materials for the project and assemble the prototype. This applies only to the USB interface and radar module. Once the subsystems have been assembled, another phase of testing will be required. This is to verify all the parts are working as they should prior to the final assembly. Once the radar, USB interface and software have all been independently tested, the final objective is to integrate the system and attempt to reach the primary goal of the project.

It is possible that the final testing and integration stage may reveal shortcomings or issues with regard to system design. Our team's approach will be to meet the final objective as quickly as possible to leave time for circling back and making modifications to the system.

# 2.4 Requirement Specifications

#### 2.4.1 Desired System Qualities

#### 2.4.1.1 Accuracy Requirements

There are certain qualities in a product that will guide our requirement specifications. Accuracy is one important quality; our primary goal of measuring car velocities will be used as an example. If a car comes at 30 meters per second and the radar system reports 10 meters per second as its measurement, the radar is essentially useless. If the system reports 30 meters per second but only after a long delay, the radar is not much use either unless the results are adjusted for the time delay (this is not very useful for real time analysis). If the radar reports 28 meters per second with a very short delay, there is still error present, but the system is suitable for general analysis of the environment. In summary, our system needs to prioritize accurate results, but not so much as to cause excessive strain on the technical design.

The first accuracy requirement specification will be imposed on our system that says the output measurement must be between plus and minus 10 percent of the actual parameter value. This means that the system error is allowed to increase slightly as the magnitude of the measured quantity is increased, such as for very high velocities or very long distances. Verification of this requirement involves taking an accurate, external reading of the parameter in question and comparing it to the measured parameter generated by our system. This is fairly straightforward in the case of the ranging goal, for instance, where the distance can be easily measured between the radar module and a stationary object. For velocity error calculation, a calibrated commercial off-the-shelf device with a known error can be used to measure the velocity

of the target object. Alternatively, our team may choose to acquire a target that we can control the velocity of, so the accurate velocity will always be known.

The second accuracy requirement specification to be imposed on our system says that the output measurement must be generated and displayed by the software no longer than three seconds after the measured parameter occurs in the environment. This means that if a velocity of 5 meters/second appears in the environment, and then immediately disappears, it should be no longer than three seconds before the system displays 5 meters/second. In actuality, this requirement is somewhat lax, as real-time system outputs often appear nearly instantaneously. For the sake of establishing an absolute maximum lag time for our software and taking into account data transmission complexity in our anticipated subsystem architectures, three seconds will be used.

The final accuracy requirement specification has to do with the transmitted frequency. In general, as frequency is increased, accuracy of the radar increases as well. Frequency constraints will be discussed more later on, but for now, we will impose a requirement that the system must transmit at no less than 2 GHz for sufficient radar accuracy.

# 2.4.1.2 Operating Distance Requirement

Maximum operating distance is another system parameter that must be established. This is the longest length at which the radar output will remain within the maximum error requirement outlined above. The desired maximum operating distance is largely dependent on the specific application of the radar. Since our radar module is meant to be multi-purpose for the general consumer, it can be assumed that the targets are within 50 meters of the user. This means that at the very least, our radar should be able to sense targets up to 50 meters away. Being able to accurately sense anything further is not necessary, but it would be an improvement.

# 2.4.1.3 System Runtime Requirement

A characteristic similar to maximum operating range is minimum system runtime. The necessary runtime for the system is largely dependent on the application. In general, the system should remain on long enough to allow for sufficient data collection in an environment. If the system loses power soon after powering on, not only would the user have to consistently replace the batteries, but the user would not be able to collect very much successive information before having to put the module down. A minimum total runtime of 30 minutes will be the system requirement. While this does mean the radar module would not be ideal for long-term, continuous environment surveillance, it will work nicely for measuring environment parameters in short sessions.

Verification that the runtime requirement has been met is slightly tricky, since in actuality the runtime is not entirely dependent on the system characteristics. It also depends on the type of batteries that are used. Several batteries with the same voltage may have different capacities, which will then translate into different system runtimes. For the sake of catering to the general consumer, our team will use batteries that can be easily

acquired in a local hardware shop or general store. The capacities and characteristics of those batteries will be used as the standard to gauge the runtime performance of our radar module.

#### 2.4.1.4 Transmitted Power Requirement

How much power the system consumes is closely related to runtime. The more power the system consumes, the shorter the run time will be, regardless of what type of (presumably finite) power supply is used. Additionally, high-powered electrical systems have the tendency to generate excessive heat, which will be discussed further in the Health and Safety section of the paper. The primary element of our system that affects power use is the transmitted power of the radar; the other elements of the system have reasonably low current draw that will not raise a power-consumption concern. Prior knowledge and research has shown us that our desired radar accuracy can be achieved by transmitting on the order of 10 milliwatts of power. This will be set as the lower threshold for transmitted power. Although lower transmitted power is better for runtime, as will be illustrated in the House of Quality figure, on its own a high transmitted power is actually better, in general, for a radar system. For this reason, a lower threshold for transmitted power is established, and the proper balance must be found between using a higher power and compromising other elements of the system.

#### 2.4.1.5 Module Size Requirements

Portability is an ideal characteristic for our system. The basis is simple: the end-user should be able to pick up the radar module and point it in different directions. This makes it easier to take multiple measurements in an environment without the hassle of moving a large piece of equipment. Two parameters that affect portability are weight and dimensions. The requirements for these two parameters will be set to less than 3 kilograms and less than 0.5 cubic meters, respectively.

#### 2.4.1.6 System Cost Requirement

The final characteristic to be considered is cost. Radar systems are relatively expensive when compared to other systems in electrical engineering due to the high cost of RF signal processing components. Our budget for the project, which is almost entirely dependent on the cost of the hardware, will take into account both hardware costs and each team member's maximum contribution to the project. The requirement for cost therefore states that in total, the system must cost no more than \$800.

# 2.4.2 Requirements Summary

Table 1 below summarizes the quantitative requirements discussed in the previous section. Note that measurement error is the only requirement with both an upper and a lower bound, denoted this way for clarity. Another way of stating it is that the absolute value of the measurement error must be no greater than ten percent of the actual parameter value.

Table I FMCW Radar Requirements

| FMCW Radar Requirements |               |                  |  |  |  |

|-------------------------|---------------|------------------|--|--|--|

| Requirement             | Minimum       | Maximum          |  |  |  |

| Measurement Error       | -10%          | +10%             |  |  |  |

| Max Operating Distance  | 50 meters     |                  |  |  |  |

| Runtime                 | 30 minutes    |                  |  |  |  |

| Cost                    |               | \$800            |  |  |  |

| Size                    |               | 0.5 cubic meters |  |  |  |

| Frequency               | 2 GHz         |                  |  |  |  |

| Output (TX) Power       | 10 milliWatta |                  |  |  |  |

| Software Lag Time       |               | 3 seconds        |  |  |  |

| Weight                  |               | 3 kilograms      |  |  |  |

# 2.4.3 House of Quality

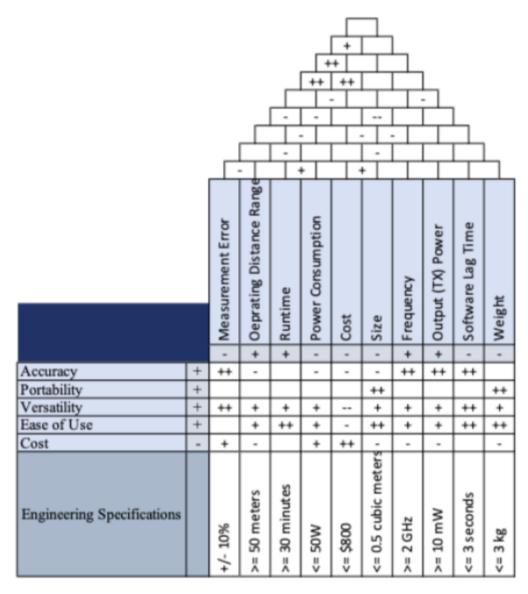

Designing a marketable consumer product involves finding a good balance between conflicting consumer desired qualities. Every desired quantity cannot be maximized, because increasing one will inevitably decrease another. For instance, if the cost of the system is very low, it will inevitably cause the system accuracy to become low as well. High accuracy means purchasing high-quality parts, and high-quality parts are more expensive than low-quality parts. It becomes a balancing act between desired qualities.

The house of quality for our system, shown in Figure 1, shows the relationship between all the desired system qualities and the technical characteristics of the system. On the left side of the figure, each quality is listed with a plus or a minus sign, depending on whether the quality should be as high as possible or as low as possible, respectively. The top of the rectangular portion of the figure shows the technical characteristics of the radar system, and whether they should ideally be as high as possible (indicated with a plus sign) or as low as possible (indicated with a minus sign).

The intersection between a quality and a technical characteristic shows how moving the technical characteristic in the ideal direction would impact the quality parameter. The "roof" of the house of quality shows the interrelationship between the technical characteristics.

Note that some intersection points in the figure are blank. This indicates that there is no relationship between the intersecting characteristics. Technical characteristics with many plus signs in their corresponding intersection points can be easily moved in the desired direction without much impact on other parameters. For our specific project, measurement error and software lag time are two technical characteristics whose intersection points with other parameters are mostly blank squares and plus signs. This means the software lag time and measurement error can both be decreased as desired, and other system parameters will either be benefitted or remain unaffected.

Fig. 1. FMCW radar project house of quality.

# 3.0 Project Research

# 3.1 Radar Background Theory

# 3.1.1 Radar Transmission Theory

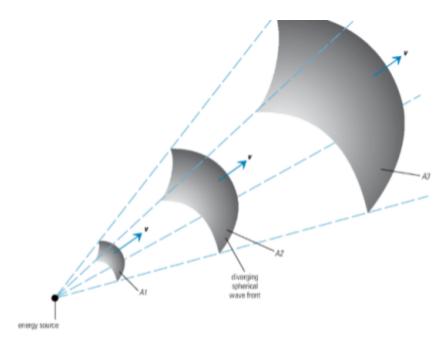

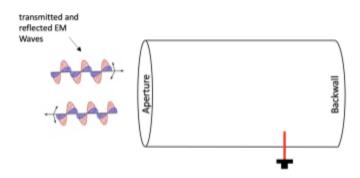

The doppler in our system consists of an oscillator that after some attenuation amplification, gets split in two, where transmitted, the other half is fed into a frequency mixer which performs a multiplication function. The transmitter emits a microwave spherical wavefront, as shown in Figure 3. We could imagine this spherical wavefront

propagating from the emitter and reaching a target downrange. Some of the wavefront intersects with the cross-section of the target and is scattered back to the emitter.

Fig. 3. Spherical wavefront.

In order to reduce the coupling between the transmitter and receiver and avoid deadening the received signal we have separated the two. In conventional radar systems one usually would have only one.

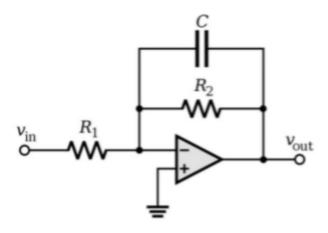

The received scattering is then amplified and fed into the multiplier. The difference comes out of the mixer and is amplified with three op-amps. The three op amps consist of an amplifier and a fourth-order low-pass filter.

The range to the object is calculated by determining the round-trip distance that light would have traveled in that amount of time. Note that signal power drops by the distance to the object raised to the fourth power. This tells us that the farther an object is, the more difficult it is to distinguish the received power pulse from the noise.

Below is the equation for range in a two-way (roundtrip) radar.

$$Range \simeq \frac{P_t G_t G_R \lambda^2}{(4\pi)^3 S_{min}} \tag{1}$$

$P_{t} = transmitted power$   $G_{t} = transmitted antenna gain$   $G_{p} = receiver antenna gain$

$\lambda = wavelength of signal$   $S_{min} = minimum detectable signal$

The gain of antenna is given by

$$G = \frac{4\pi A_e}{\lambda^2} \tag{2}$$

$A_{\rho} = equivalent area of aperture$

Substituting into Equation (1) results in

Range

$$\simeq \left(\frac{P_t \sigma \pi r^2}{2\lambda^2 S_{min}}\right)^{1/4}$$

(3)

We can observe based on the above equation that in order to double the range of a range system we would need to increase its power by a factor of 16. We could also increase the frequency by a factor of 4, or double the radius of the aperture. Understanding the technical background of our product lets us have a deeper insight into the design choices and how to improve the product in future iterations.

To minimize range ambiguity we want to ensure the distance to the target is greater than or equal to the speed of light divided by two times the pulse repetition frequency.

Distance

$$\geq \left(\frac{c}{2^*(Pulse\ Repetition\ Frequency)}\right)$$

(4)

#### 3.1.2 Microwave Theory

There are fundamental differences between traditional circuit and network theory and microwave engineering theory. In the traditional circuit model a circuit is described by how much energy is guided through interconnected components. The sizes of the components do not matter in their function, and the voltage is the same along a transmission line. In network theory the ratio between voltage and current is always a constant. We are able to use Kirchhoff's laws to solve for unknown values in a straight-forward way. The ratio of voltage to current is called impedance. We can model resistors, inductors, and capacitors using impedance. In order to model sinusoidal time variance complex impedance can be used. When signals are traveling through a line, only one mode can propagate.

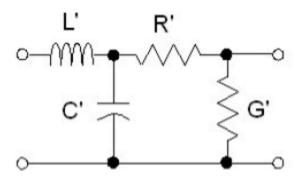

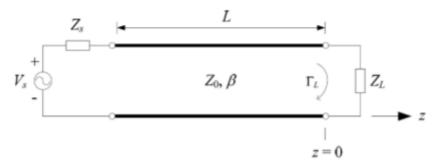

We can model an infinitely small cross sectional area of a transmission line with the generalized lumped-element model of a transmission line, as shown in Figure 4. This model allows us to calculate characteristic impedance, phase velocity, and both the real and imaginary parts of the propagation constant.

Fig. 4. Generalized lumped-element model.

The relationships between the wavelength, phase velocity, and phase constant are useful to understand. The relationship between wavelength and the phase velocity is given by

$$\beta = \frac{2\pi}{\lambda} \text{ (radians/length)} \tag{5}$$

where  $\beta = \omega \sqrt{L'C'} = 2\pi f \sqrt{L'C'}$

The series impedance and shunt admittance are given as

$$Z' = R' + j\omega L' \tag{6}$$

$$Y' = G' + jwC'$$

(7)

The propagation constant is given as

$$\gamma = \sqrt{Z'Y'} \tag{8}$$

The characteristic impedance of a transmission line can be found understood using the following equations.

$$Z_0 = \sqrt{\frac{R' + j\omega L'}{G' + j\omega C'}}$$

(low-loss) (9)

For lossless transmission lines the following wave equations can be used to derive the phase velocity.

$$-\frac{\partial v(z,t)}{\partial z} = L\frac{\partial i(z,t)}{\partial t} \rightarrow \frac{\partial v^2(z,t)}{\partial z^2} - \frac{1}{v_p^2} \frac{\partial v^2(z,t)}{\partial t^2} = 0$$

(10)

$$-\frac{\partial i(z,t)}{\partial z} = C \frac{\partial v(z,t)}{\partial t} \rightarrow \frac{\partial i^2(z,t)}{\partial z^2} - \frac{1}{v_p^2} \frac{\partial i^2(z,t)}{\partial t^2} = 0$$

(11)

This leads to

$$v_p = \frac{1}{\sqrt{L'C'}} \tag{12}$$

The general solution for a lossless transmission line is given as

$$v(z,t) = v^{+}(t - \frac{z}{v_{p}}) + v^{-}(t + \frac{z}{v_{p}})$$

(13)

$$i(z,t) = i^{+}(t - \frac{z}{v_{p}}) + i^{-}(t + \frac{z}{v_{p}}) = \frac{v^{+}(t - \frac{z}{v_{p}}) - v^{-}(t - \frac{z}{v_{p}})}{Z_{0}}$$

(14)

$$Z_0 = \sqrt{\frac{L}{c}}$$

(characteristic impedance) (15)

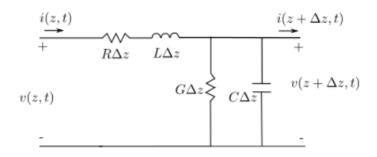

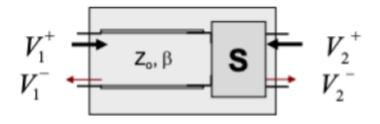

For time harmonic transmission lines (illustrated in Figure 5)

$$\frac{dV(z)}{dz} = -(R + j\omega L)I(z) \to \frac{dV^{2}(z)}{dz^{2}} - (R + j\omega L)(G + j\omega C)V(z) = 0$$

(16)

$$\frac{dI(z)}{dz} = -(G + j\omega C)V(z) \to \frac{dI^{2}(z)}{dz^{2}} - (R + j\omega L)(G + j\omega C)I(z) = 0$$

(17)

Figure 5: Time Harmonic Transmission Line.

$$Z_0 = \sqrt{\frac{L'}{C'}} \tag{18}$$

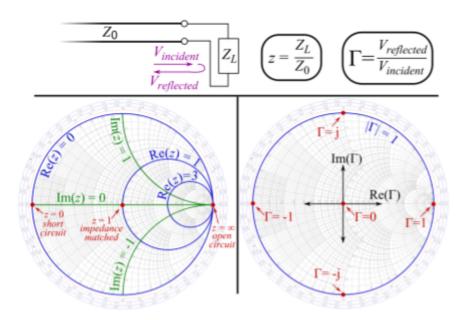

The standing wave ratio measures the impedance matching of the loads to the characteristic impedance of the transmission line. Standing waves will be created when the impedance is mismatched. The standing wave ratio is given by

$$SWR = \frac{V_{max}}{V_{min}} = \frac{1 + |\Gamma|}{1 - |\Gamma|}$$

(19)

Voltage on a transmission line is described by

$$V(z) = V_0^+ (e^{-j\beta z} + \frac{V_0^-}{V_0^+}) = V_0^+ (e^{-j\beta z} + \Gamma_L e^{+j\beta z})$$

(20)

$$I(z) = \frac{V_0^+}{Z_0} \left( e^{-j\beta z} - \frac{V_0^-}{V_0^+} e^{+j\beta z} \right) = V_0^+ \left( e^{-j\beta z} + \Gamma_L e^{+j\beta z} \right)$$

(21)

For reflection, a transmission line terminated in a short or open reflects all power back to the source. When considering input impedance (illustrated in Figure 6),

Fig. 6. Input impedance.

$$Z_{in} = \frac{V(z)}{I(z)} = Z_0 \frac{1 + \Gamma_L e^{+j2\beta z}}{1 - \Gamma_L e^{+j2\beta z}}$$

(22)

$$Z_{in} = \frac{V(z)}{I(z)} = Z_0 \frac{1 + \Gamma_L(l)}{1 - \Gamma_I(l)}$$

(23)

This gives,

$$\Gamma_{L}(l) = \frac{Z_{in} - Z_{0}}{Z_{in} + Z_{0}}$$

(24)

Note that L' can be thought about as the tendency of a transmission line to oppose a change in current. Conversely, C' can be thought about as the tendency for a transmission line to oppose a change in voltage. The phase velocity can also be found if we know L' and C'.

$$v_p = \frac{1}{\sqrt{L'C'}} \tag{25}$$

#### 3.1.3 Antennas and Electromagnetics

An antenna can convert a signal voltage on a transmission line into a transmitted electromagnetic wave. A time varying signal applied to the transmit antenna induces an electrical current on the antenna which in turn produces electromagnetic radiation. Antennas are dielectric or metal structures that are specifically designed or chosen to provide an efficient launch of electromagnetic waves into space. Physically, we can conceptualize an antenna as providing a sea of free electrons which can be influenced by external forces and that offer zero resistance to movement.

We can derive from Maxwell's equations that electromagnetic radiation occurs when electric charge accelerates. We cannot directly see electromagnetic waves. In order to prove they exist, we can formulate Maxwell's equations as a wave equation in the form

$$\nabla^2 \Psi - \frac{1}{v^2} \frac{\partial^2 \Psi}{\partial t^2} = g \tag{26}$$

where  $\Psi$  is the field quantity. Next, we take the curl of Faraday's law to obtain the new vector field as

$$\nabla x \nabla x E = -\nabla x \frac{\partial B}{\partial t} = \frac{\partial}{\partial t} (\nabla x B)$$

(27)

$$\nabla x \nabla x E = -\nabla x \frac{\partial B}{\partial t} = -\epsilon \mu \frac{\partial^2 E}{\partial t^2} - \mu \frac{\partial J}{\partial t}$$

(28)

The right hand side of the above equation yields some important observations. In free space J=0 and  $\epsilon=\epsilon_0$ . Therefore

$$v = c = \frac{1}{\sqrt{\epsilon_o \mu_0}} \tag{29}$$

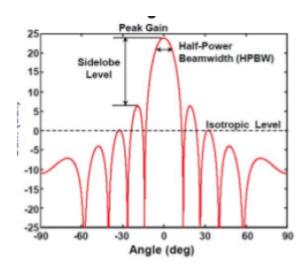

As the electromagnetic wave traveling at the speed of light reflects off of an object, the reflected energy illuminates the receiving antenna which in turn induces a signal that travels through a coaxial cable. For an isotropic antenna, the electromagnetic wave propagates spherically from the excitation point. A directional antenna (which is the type our system uses) produces a gain radiation pattern as shown in Figure 7.

Fig. 7. Gain pattern for circular aperture.

Note that a directional antenna has a main beam that is pointed in a direction and sidelobes that radiate away from the beam. The electromagnetic waves are not sent in a perfectly circular beam. As the antenna diameter increases, the bandwidth gets narrower and the main beam's gain increases. The gain G of an aperture is given by the expression.

$$G = \frac{4\pi A_e}{\lambda^2} \tag{30}$$

The effective isotropic radiated power is a function of the transmitted power and the gain of the transmitting antenna.

When considering calculating the gain from measured power coupling between two identical antennas we can utilize the following relation.

$$G_{dBi} = \frac{1}{2} \left[ 10 \log(\frac{P_r(\theta, \varphi)}{P_r}) + 20 \log(\frac{4\pi r}{\lambda}) \right]$$

(31)

The voltage reflection coefficient tells us how much of the signal is reflected by the antenna. Note that for a well-designed antenna the magnitude of the voltage reflection coefficient should have a low value. The power transmission coefficient tells us how much power is transmitted relative to the incident power.

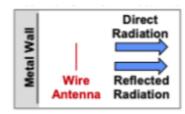

If a wire is placed next to a metal wall, the antenna radiation will have a phase shift of 180 degrees. If we want our radiated energy to efficiently be directed in a direction, we would place our antenna a quarter of a wavelength away from the metal wall, causing the phase shift to now be 360 degrees (see Figure 8). In a circular waveguide  $TE_{11}$  mode will be used.

Fig. 8. Wire antenna near a PEC barrier.

In summary we have described some of the fundamental characteristics of antennas. We have also described the design of a circular waveguide antenna that can be used as a transducer, as shown in Figure 9.

Fig. 9. Diagram of a "cantenna" antenna.

Here are the dimensions of the coffee cans we are using:

- ➤ Metal Can Length = 5.25"

- ➤ Metal Can Diameter = 3.9"

- ➤ Monopole Wire Length = 1.2"

- Spacing from monopole wire to back wall = 1.8"

An analog to digital converter will need to be implemented to digitize the phase differences for further signal processing.

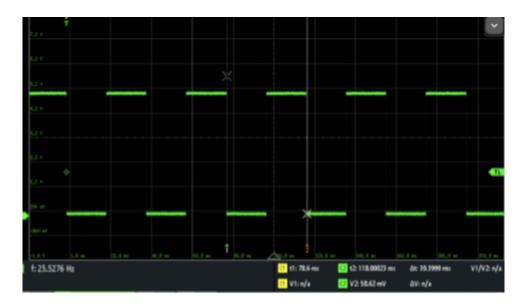

The modulator will be able to select what mode the radar is in. The square wave mode will select velocity mode for the radar. The square wave is sent into the VCO. This creates a tone signal, this is then sent to the transmitter and bounced off an object moving at a certain velocity. This reflected signal will come back into the receiver antenna with a frequency shift. This signal is then mixed with the original transmitted signal. The lowpass filter selects the difference frequency. This is then going to be sent to the laptop or microcontroller where it will undergo a fast fourier transform. Our note that our FMCW radar is an active system, being powered by 9V batteries.

#### 3.2 Similar Products

During our market search we found the following relevant products available.

#### 3.2.1 MIT Small Radar System

Our initial product design used the MIT Small Radar System as a reference point for the initial design of our product. The setup uses a radar module to interface with a laptop via a two-channel audio cable, which has a 3.5mm audio jack on the laptop side. Key characteristics of the radar module itself are its FMCW architecture, coffee-can receive and transmit antennas, and S-band range of operation. The primary area of the project our team will be improving upon is the communication interface. Firstly, the MIT setup uses post-data acquisition processing. A .wav file is recorded while the radar is running, and the entire .wav file is analyzed digitally after the radar module has been turned off. Our project will provide real-time data processing capabilities, eliminating the need to record and store large files on the host device. Additionally, the audio cable used in the MIT laptop-based radar is effective but not ideal, as the majority of devices that interface with laptops do so via USB. Our project will increase flexibility by changing the audio cable to a USB2 cable. Elements of the MIT design that will remain largely similar in our design include the active gain stage, active low pass filter, and applications (doppler and ranging).

# 3.2.2 Police Radar Systems

Police radar systems are devices used to track the velocity of vehicles. Though such devices are available on the market, they are typically quite costly, ranging from \$500 to \$2000. Our system will be able to track velocity at a much lower cost. This will allow our product to reach an untapped market for consumers who wish to have the functionality of a velocity radar system without the steep cost. One difference between our system and police radar systems is that police radars typically operate in several frequency ranges including the X band( $\approx 10.5 \, \text{GHz}$ ), K band( $\approx 24 \, \text{GHz}$ ), and Ka band( $\approx 33-36 \, \text{GHz}$ ) [18]. The primary reason for using these bands would be due to the fact that for higher frequencies, smaller antennas can be used, therefore maximizing space efficiency. To facilitate testing of our project, we will operate in a lower band where design components are a bit easier to obtain. Additionally, specific bands require licensing to use, and this must be taken into consideration for the purposes of our project demonstration.

#### 3.2.3 Automatic Doors

Automatic doors operate by using a sensing system to send signals to a control system that will open the door for oneself. These sensing systems come in many different forms, but at a fundamental level sensing systems will be detecting disturbances within an electromagnetic field.

Our system will encode the received information in a digital format. This allows the potential for digital signal processing and integration with other systems. In theory one will be able to use our system to interface to a control system such as an automatic door. Automatic door installation on the market will run one on the order of thousands. Our system would allow savvy consumers the ability to use the data from our radar for various sensing and controls applications.

# 3.3 Relevant Technologies

## 3.3.1 Remote Sensing

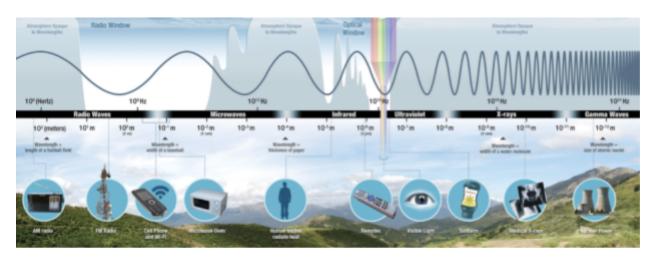

When discussing technologies such as remote sensing, electromagnetic energy travels in the form of waves through free-space. The wavelengths can vary from the order of millimeters to kilometers, as illustrated in Figure 10. We are all familiar with visible light, which sits somewhere towards the middle of the electromagnetic spectrum. Visible light only covers a very small portion of the electromagnetic spectrum. We need instrumentation to observe any other forms of electromagnetic energy.

Remote sensing is the process of measuring the reflected and emitted electromagnetic energy at a distance; without contact. These measurements can be used to detect and monitor the physical characteristics of an object of interest. The required spectral, radiometric, and spectral resolutions will vary based on the desired application.

Fig. 10. Diagram of electromagnetic spectrum. Credit: NASA Science.

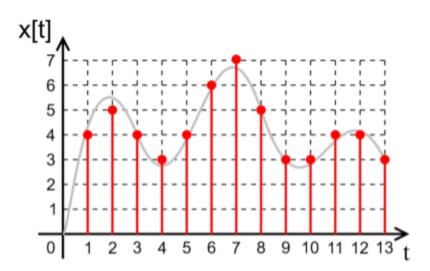

#### 3.3.2 Pulse-Doppler Signal Processing

Our system will be able to determine the range of an object using Pulse-Doppler Signal Processing. This process utilizes the Doppler effect which describes the change in frequency of a wave in relation to an observer who is moving relative to the wave source. We frequently hear this phenomenon in our daily lives when we hear a car horn or police siren change pitch as it drives away or towards us.

It is important to recognize that we are not directly measuring the frequency shift, but are measuring the phase shift between pulses.

As the object that is reflecting the electromagnetic waves moves in position, the returned signal carries a phase difference relative to the previous pulse. This principle allows us to translate the information to electrical signals and ultimately compute range.

#### 3.3.3 Transceiver Architectures

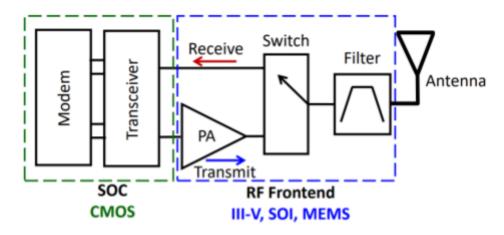

A basic radio system at a fundamental level, has a transmitter to propagate the electromagnetic wave carrying the signal and also a receiver to obtain these waves being propagated within the air. The transmitter will generally have a modulator that will combine a low frequency signal with the high frequency signal, using a mixer. The receiver will serve the opposite function of demodulating the signal and obtaining the signal at hand and then provide the system information sent over from a transmitter. There are 2 popular types of radio systems, which are the following: the Time-Domain Duplexing (TDD) and the Frequency-Domain Duplexing (FDD).

#### 3.3.3.1 Time-Domain Duplexing Model

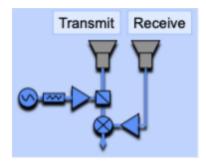

The TDD (shown in Figure 11) is a progressing area in the current area of 5G communication since it provides better quality signals for this range. The system on chip, is based on complementary mosfet technology (CMOS) which includes the modem and transceiver of the overall system. The RF frontend where we primarily work with high frequency signals is at a very base level composed of the power amplifier (PA), switch (III-V semiconductors, MEMS, etc.), and filter. This system is nice and convenient to implement since we are able to use a switch to swap from transmit or receive mode.

Fig. 11. The time-domain duplexing model.

## 3.3.3.2 Frequency-Domain Duplexing Model

The Frequency-Domain Duplexing (FDD) shown in Figure 12 has both transmission and receiving operating at the same time. It similarly has the CMOS technology for the SOC and the III-V compounds & MEMS for the RF frontend. 4G-LTE bands generally depend on this system to operate.

Fig. 12. The frequency-domain duplexing model.

Above we discussed a very high level understanding of the 2 techniques of the transceiver architectures. If we go further in detail, the system becomes increasingly complicated. The receiver system and transmit system have their own block diagrams, and the receiver is generally much more complicated than the transmit. This would because the receiver must deal with interferers, noise, non-linearity, dynamic range, etc. Generally, there are 3 different receiver architectures that we would consider. These are the Direct Conversion (RF to Low Frequency), Heterodyne (RF to IF [Intermediate Frequency] to Low Frequency), and the Super Heterodyne (RF to IF2 to IF1 to Low Frequency).

#### 3.3.3.3 Direct Conversion Receiver

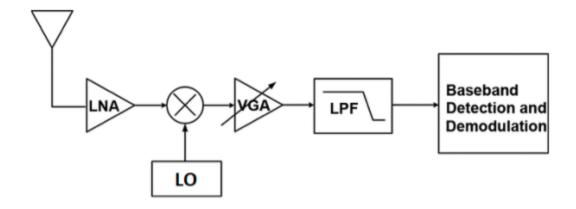

A direct conversion receiver, shown in Figure 13, demodulates the radio frequency signal using synchronous detection with a local oscillator that has a frequency close to the carrier frequency of the signal. This simple system is good, for overall simplicity of circuit design. Though the issue using this technique would be dynamic range. This technique was initially useless in its initial conception due to errors you may receive in the signal. Modern technology has allowed this to be considered again because of corrections that can be made with the aid of software.

Fig. 13. A direct conversion receiver.

#### 3.3.3.4 Heterodyne Receiver

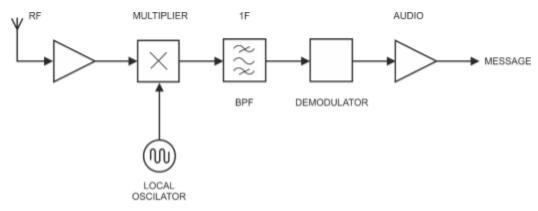

A heterodyne receiver, shown in Figure 14, makes the use of an intermediary frequency signal and then into the low frequency territory. We are able to make use of this by using one mixer to bring a modulated RF signal to the modulated IF signal, which when demodulated brings us to baseband signal. The main reason we would want to use the intermediate frequency is to improve the frequency selectivity. Since radio frequency is really used in some form of communication circuits, we generally would like to easily pick out the desired signals and this would require filtering. The better the frequency selectivity, the better it is to pick out our desired signal. Finally, there is the super heterodyne receiver which makes use of 2 different intermediate frequency conversions. This would therefore cause us to use 2 mixers in the system actually. The primary reason we would want to use a system like this is to better tune the frequency selectivity than with just 1 IF conversion. We would first go from RF to the first IF which is "high" then to the second IF which is "low" and then finally to the low frequency signal.

Fig. 14. A heterodyne receiver

# 3.4 Strategic Components and Part Selections

In order to strategically select our components and part selections, it is important to have some understanding of transmission line theory, as at high frequencies circuits behave much differently than at low-frequencies as seen in linear circuits theory.

Also, in order to properly understand the operation of the radar, it is important to make sure we are informed of the relevant theory that would help us visualize how the various components are working together in order to make the system function.

#### 3.4.1 RF Signal Processing Components

Our RF signal processing components were chosen to meet the following parameters.

- > Frequency = 2.4Hz

- ➤ Bandwidth = 80MHz

- ➤ Antenna Isolation = 50dB

- ➤ DC Power < 1W

- > RF Power < 1W (EIRP)

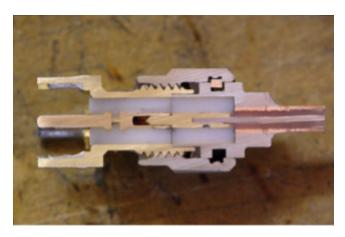

Some realization constraints were inherent in our design. We wanted the system to be able to use off the shelf parts, use connectorized components, and run on 9V batteries. On the transmitted side we needed a modulated source, amplification, distribution, and an antenna for radiation. On the receiver end we needed an antenna to receive aperture, amplification, and a demodulator.

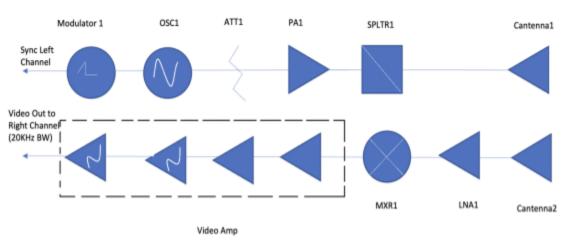

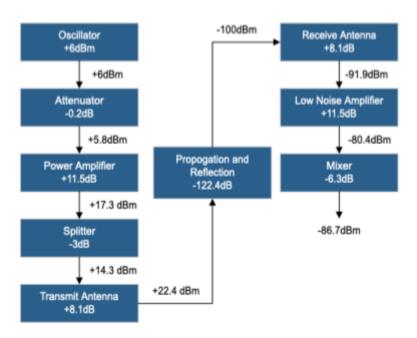

The transmitting RF component chain is made up of a cascaded two-port network model that consists of a VCO, attenuator, amplifier, splitter, and finally transmitting antenna. The receive chain consists of the receiving antenna, amplifier, and finally the mixer.

The receiving and transmitting antennas are dubbed the cantenna's due to the fact that cans were used as the circularly polarized waveguide antennas. These antennas are surprisingly highly efficient and suit our purposes very well. In order to understand the RF and antenna subsystem, it is worthwhile to describe some of the fundamental characteristics of antennas. We want to develop a stronger understanding of gain radiation patterns, power density, beamwidth, reflection coefficient, transmission coefficient, antennas arrays, measurements. We will use this understanding to follow the design, fabrication, and testing of an antenna that can be used as a transducer.

# 3.4.2 RF Design Description

The RF section of our hardware design will consist of a voltage controlled oscillator that is fed into an attenuator the signal is then amplified and sent through a beam splitter. Half of the signal will be transmitted, and the other half will be sent to the mixer. Once the signal is received the received signal will be amplified and then multiplied with the

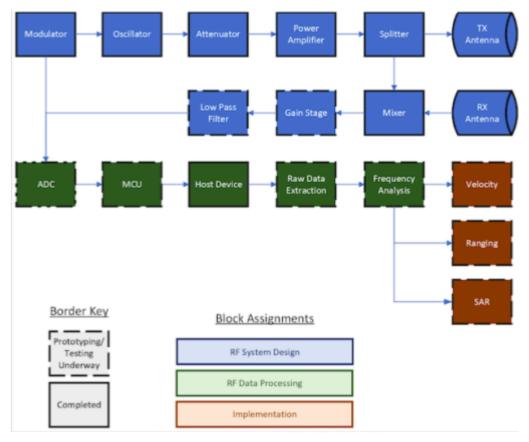

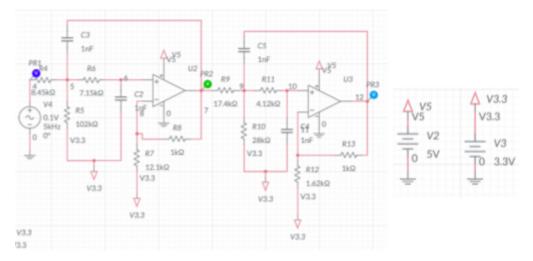

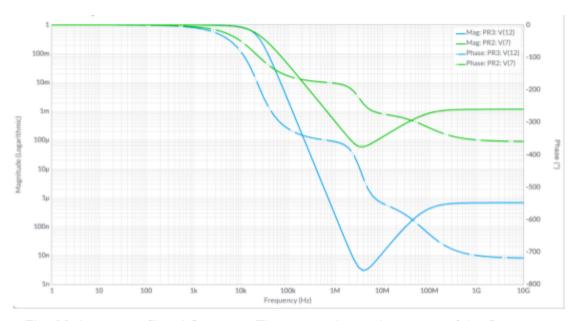

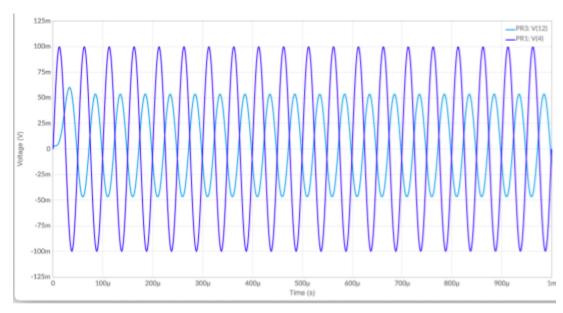

reference signal that was sent into the mixer. The signal is then sent through a gain stage and then low-passed to prevent aliasing. This signal will be sent for further signal processing. This architecture is illustrated in Figure 15.

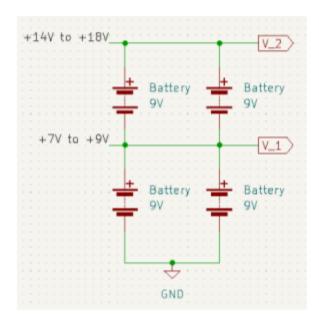

The system will be powered with a 9V battery pack, producing +9V and +18V. This powers the RF components and provides a reference voltage for the analog circuits The +5V will power analog circuits including the modulator, gain stage, and fourth order low pass filter.

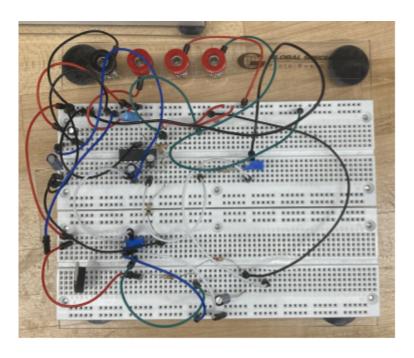

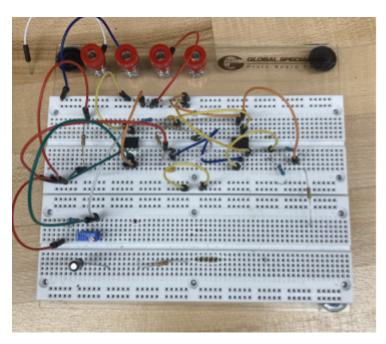

Our next steps will include building the system on a breadboard and starting the testing phase.

Fig. 15. RF hardware setup.

We will be using the ZX95-2536C+ Voltage Controlled Oscillator, the ZX60-272LN-S+ Low Noise Amplifier, the ZX10-2-42+ 0.1dB insertion loss splitter, and the ZX05-43MH-S+ Mixer.

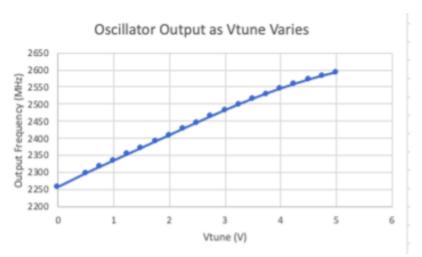

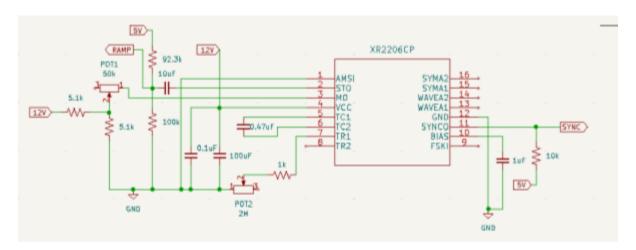

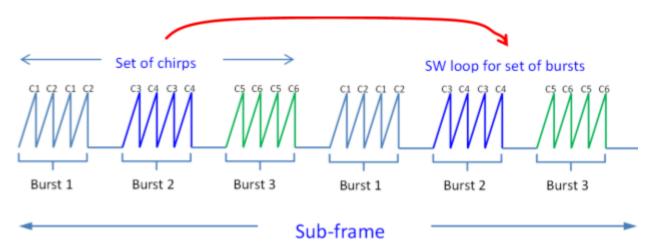

#### 3.4.3 Modulator

The modulator is what will be driving our transmitted signal. We will use an integrated chip that would be able to produce various waveforms such as ramp, sine, and square. For the purposes of range and velocity sensing we will be using a ramp waveform. Our modulator would modulate oscillator 1 yielding a voltage that is proportional to the transmit frequency. The modulator also provides a syncing function.

The Vtune voltage in the modulator will be proportional to the transmit frequency. The linear ramping of the voltage of the modulator will cause the oscillator to produce a linear FM chirp that is used for transmitting and receiving. The ramp time will be approximately 20ms with a triangular wave period of 40ms. The magnitude of the ramp will modulate the desired transmitted bandwidth.

For the high frequency modulation, we are using a ramp generator to modulate the low frequency information. The XR-2206 is a monolithic function generator which we will use to create our modulating signal in the low frequency range. This component is capable of creating high quality sine, square, triangle, ramp, and pulse signals that have

high stability and accuracy. This specific application we would like the XR-2206 to produce a ramp signal, which is popular to use in communication systems. Ramp generators are very popular to use since they provide a quick response and provide the capability to change the start-up & return flow time. The "Sync Pulse Inhibit" is a feature of the circuit since we would like to have a functionality that allows the converter to be turned off and on without having the cycle power. This would help up therefore, save power, reducing inrush current, help prevent input impedance problems and delay the converter turning on before the voltage stabilizes. The frequency space portion of the ramp generator is meant to help us adjust the frequency range we would like to use on the circuit based upon what range we would like to create the ramp at and will be manually done here with a potentiometer. The chirp rate adjust part is what the name implies, adjusts the rate of the chirp seen on the low frequency end. A chirp is generally defined as a signal where the frequency either increases or decreases over time. This specific part of a circuit is common to sonar, radar and laser systems since they are generally sending signals out to be transmitted and received. We also see the use of decoupling by the XR-2206 which is a common component to put near any integrated circuit since it protects the IC from any instantaneous changes in voltage and filters out unwanted noise that interferes with the IC outside of the system.

#### 3.4.4 Mixer

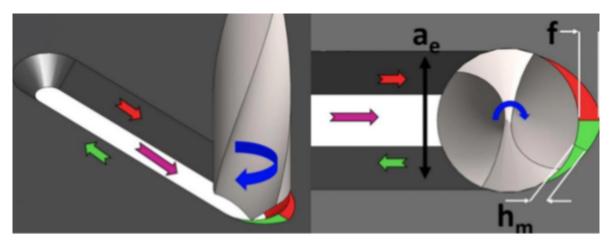

Mixers are a popular IC to use in RF communication systems. Applications of interest include military radar, cellular base stations, etc. A RF mixer can be a 3-port passive or active device that is integrated in the modulator or demodulator. The ideal goal of the mixer is to change the frequency of the electromagnetic signal, preserving the signal as much as possible (phase and amplitude). As we have discussed earlier, a mixer is a fundamental part for the heterodyne receiver models that converts RF signals to IF.

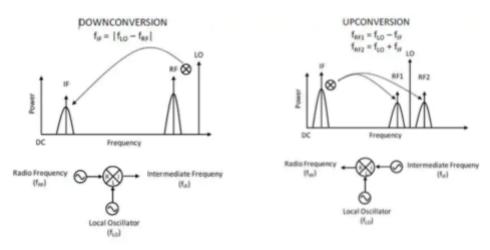

There are 2 primary conversions that the mixer is used for, downconversion and upconversion (see Figure 16). Downconversion is best described as the frequency conversion process where a radio frequency signal is mixed with the frequency coming from a local oscillator to receive the intermediate frequency to better obtain the signal integrity of the system. This process is typically done when we are interested in demodulating the desired signal at hand. Up-conversion is the reciprocal process where you combine the IF signal with the signal from the local oscillator in the frequency domain and convert it to an RF signal.

Passive mixers generally are more popular to use since they are simple in design, have a relatively large bandwidth and have good intermodulation distortion performance. Active mixers are really only used in RFIC design. Generally, active mixers provide conversion gain, good isolation between ports and do not need as much power to drive the local oscillator. They are easily able to be integrated with signal processing circuits & are not as sensitive to load matching.

Mixer parameters to be considered are conversion loss/gain, 3rd order intercept, spurious behavior, isolation, noise figure, and dynamic range. We consider conversion

loss/gain to measure the active gain or loss in a mixer. This is defined as the relationship of the IF output power to the RF input power. Conversion loss is a very important parameter for passive mixers. 3rd order intercept is the RF input power where the unwanted intermodulation signals equal to the desired IF output power. Spurious behavior is seen as external signals that create interference in the IF range. Isolation looks into the amount of power leaked from one port to another. Noise figure is a characteristic where we see how much noise (or undesired random signal) is seen from the input to the output of the mixer. Dynamic range is the power range which the mixer operates ideally.

Figure 16: (Left) Down Conversion Using a Mixer; (Right) Up Conversion Using a Mixer

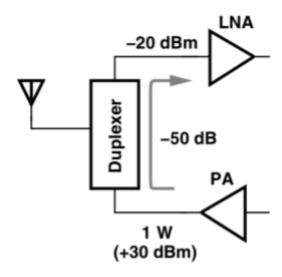

In order to choose a mixer for our project, there are a few specifications that must be established. The first is the operating frequency of the mixer. Since there are three ports on a mixer, there are three frequency specifications that should be established (typically in terms of ranges). Our mixer needs to be able to handle an RF port frequency of our radar's receive signal, which may be anywhere between 2 GHz and 2.5 GHz. It is entirely dependent on the transmit frequency the team decides on. A wider range is ideal, but the primary goal is a lower operating threshold of at least 2 GHz.

Next, the IF port frequency must be established. We wish to convert the RF signal down to the order of 10 kHz. This means our mixer must be capable of outputting this frequency on the IF port. Consequently, the mixer's LO port must be able to take an input frequency nearly identical to that of the RF port for the differential to be on the order of only 10 kHz. Another important parameter is the required power of the LO port. Mixers often have specified minimum power levels at the LO port for the mixer to operate. If this power level is excessively high, it may strain the power source of the system. A lower LO power level is generally more convenient for small-scale applications such as our project. Additional considerations when choosing a mixer is the versatility of the module, which typically refers to whether the module can work both as an upconverter and a downconverter, and the conversion loss, which should remain as low as possible.

We have decided to use the mixer suggested by the MIT OpenCourseWare course, which is the ZX05-43MH-S+ frequency mixer by MiniCircuits. Its LO and RF port frequency range is 824 MHz to 4200 MHz, which covers the 2000 MHz to 2500 MHz range needed. Its IF port ranges between DC (zero frequency) and 1500 MHz, which is more than enough for our purposes. The LO signal power is +13 dBm, which is a bit high, but ultimately this will work out nicely considering the power levels already being generated by our circuit (as will be seen in the hardware design portion of the paper). The ZX05-43MH-S+ also has a 6.1 dB typical conversion loss, which is acceptable, and very good port isolation. All around it is a great choice for our frequency mixer.

#### 3.4.5 Power Amplifier

An RF power amplifier is best defined as an electronic amplifier that is designed to take a low power RF signal and boost it up to a high power RF signal. Power amplifiers are known to drive the antenna of a transmitter generally. Important parameters for the design of a power amplifier are typically: gain, power output, bandwidth, power efficient, linearity, input/output impedance matching and heat.

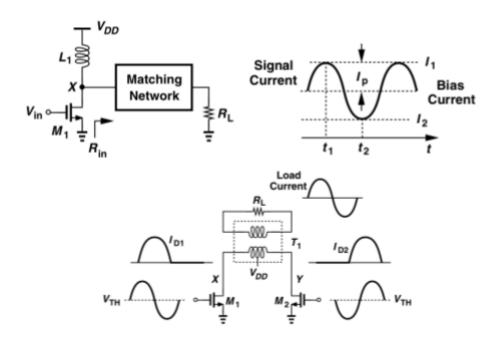

Power amplifiers are the most power consumption heavy components in a RF transceiver and provide the most difficult design challenges within the system. Basic power amplifiers include Class A, Class B, Class C, as shown in Figure 17.

Fig. 17. Top left: Class A power amplifier. Top right: Class B power amplifier. Bottom: Class C power amplifier

Power amplifiers are often placed just before a radar's transmit antenna to give the signal a final boost, and that is the use of the power amplifier in our design. Like many RF signal processing components, the most important parameter of a power amplifier is its frequency range. In our project, we need to amplify the outgoing signal at its radio frequency, which at a minimum will be 2 GHz as previously mentioned. Anywhere in the 2 GHz to 2.5 GHz range would be ideal. The second most important parameter is the amplification factor of the power amplifier, which is expressed in decibels. The MIT reference documents have suggested that the required amplification is at least 10 dB. Not only must the amplifier have the desired gain, but it must also have the ability to actually output the desired power level. A power amplifier with 10 dB of gain may not necessarily be able to output the expected 20 dBm of power from a 10 dBm input. It is important to determine the necessary output power before selecting a component.

We will use the MIT suggested MiniCircuits low noise amplifier ZX60-272LN-S+. This device has an operating frequency of between 2300 MHz and 2700 MHz, and an average gain of 14 dB, which is plenty for our purposes. One important characteristic is that this is a low noise amplifier, which helps to set a low noise factor for the entire system. This is better than a typical power amplifier, which is designed primarily for its gain characteristics and tends to have poorer noise characteristics. Though this component is called a low noise amplifier, it is functioning as a power amplifier in terms of where it is placed in the radar system.

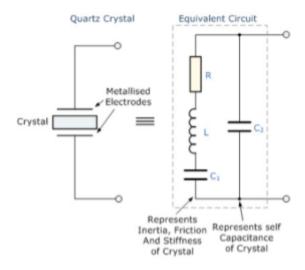

#### 3.4.6 Oscillator

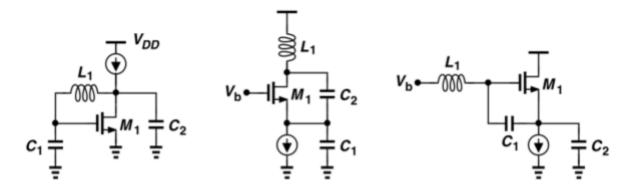

Oscillators are a fundamental part of the RF transceiver architecture. They are extensively used in both the transmit and receive paths of the system. An oscillator used in a RF transceiver must satisfy 2 primary sets of requirements: system specifications and interface specifications. System specifications relate to the frequency of operation and the signal integrity of the output. Interface specifications relate to the drive of the oscillator or the output swing. Figure 18 shows three different oscillator topologies.

RF oscillators should ideally be designed such that the frequency range can be tuned across a set range. The two sets of criteria to fit the frequency range would be, the system specification of the oscillator needed to go into the mixer and second would be an additional margin to cover process and temperature variations and errors due to modeling inaccuracies. Output voltage swing is a strong consideration as well for oscillators since they must be able to produce sufficient swings on the output to guarantee the switching of transistors for the consecutive stage. A buffer could be used to amplify/drive to drive the stages. Driving is also an important feature for oscillators as well since we would need them to be able to drive a large load capacitance. Capacitive loading is more serious in transmitters, since the input capacitance of a power amplifier can propagate to a local oscillator of upconversion mixers.

Fig. 18. Topology of 3 Different 3-Point Oscillators

Regarding the basic principles of an oscillator, an oscillator generates a periodic output. This creates a necessity for the circuit to have a system in place that allows its own noise to grow and then become a periodic signal. From the controls system point of view, an oscillator can be viewed as a system that is a "poorly designed" negative feedback amplifier. Baurkhausen's criteria states that the following condition must be satisfied to ensure stability of the oscillator:

$$|H(s = j\omega_1)| = 1$$

$\angle H(s = j\omega_1) = 180^{\circ}$

The oscillator in our circuit may be the most important component in the radar module. Since it generates the transmitted signal, it is crucial that the correct component be selected. The frequency range must, of course, contain the desired transmit frequencies. The oscillator should also be able to output voltages across the desired range. The harmonics created by the oscillator should be kept to a minimum, as well as the DC operating power. Our team has decided to use the MIT recommended part, MiniCircuit's ZX95-2536C+. This component has a frequency range of 2315 MHz to 2536 MHz, which meets the primary requirement of being higher than 2 GHz. However, the operating bandwidth of this device is the narrowest of all the RF signal processing components at only 221 MHz. This imposes a restriction on what frequency bands can be chosen for the radar's operation. Though this component will suffice for project development, this would be an excellent area for the project to be improved in. Increased frequency range is generally a positive when it comes to radar modules.

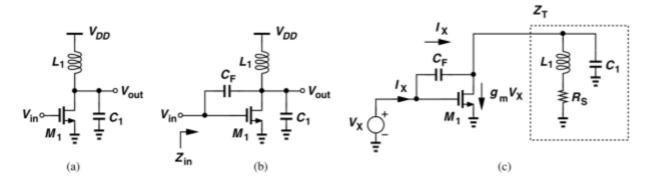

## 3.4.7 Low Noise Amplifiers

A low noise amplifier (LNA), is an RF amplifier that is designed to amplify a low power signal without degrading the signal-to-noise ratio. In an ideal since it is what it should do, but it will add noise to the signal due to the noise figure of the integrated circuit itself. An LNA generally adds about 2dB or 3dB to the signal in noise. Gain is another critical parameter for the low noise amplifier since it must be large enough to minimize the noise of the following stages. This becomes a specific issue in downconversion mixers. The choice of this gain largely depends on a compromise between noise figure and then the receiver linearity. Common topologies for an LNA include those shown in Table 2.

The most commonly used topology is the common-source stage with cascode, inductive load and inductive degeneration. Table 2 and Figure 19 show some common topologies for a low noise amplifier.

Table II LNA Topologies

| Common-Source Stage with                                | Common-Gate Stage with                                                  | Broadband Topologies                                |

|---------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------|

| ■ Inductive Load<br>■ Resistive Feedback                | ■ Inductive Load<br>■ Feedback                                          | ■ Noise-Cancelling LNAs ■ Reactance-Cancelling LNAs |

| ■ Cascode,<br>Inductive Load,<br>Inductive Degeneration | <ul> <li>Feedforward</li> <li>Cascode and<br/>Inductive Load</li> </ul> | •                                                   |

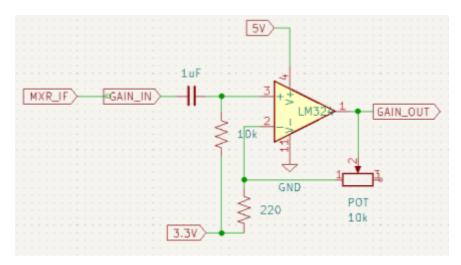

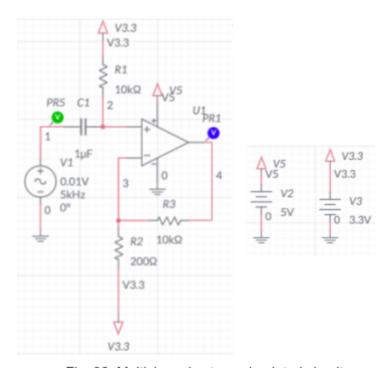

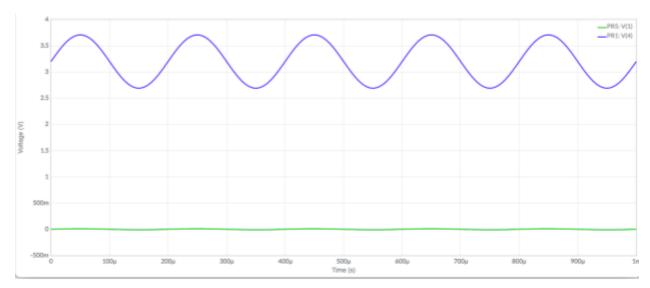

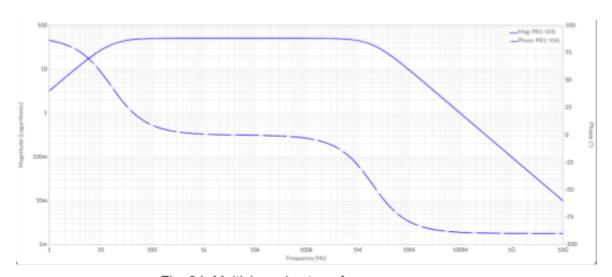

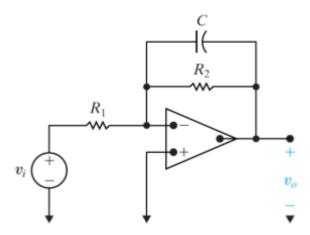

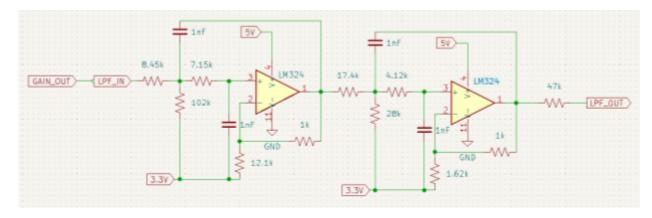

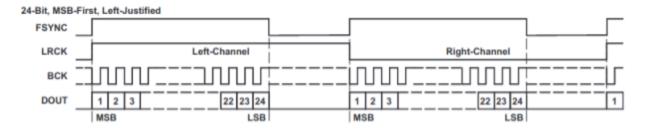

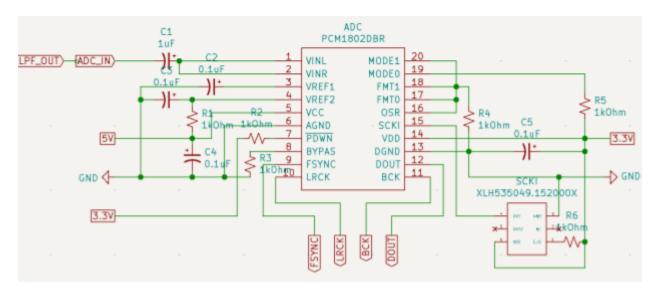

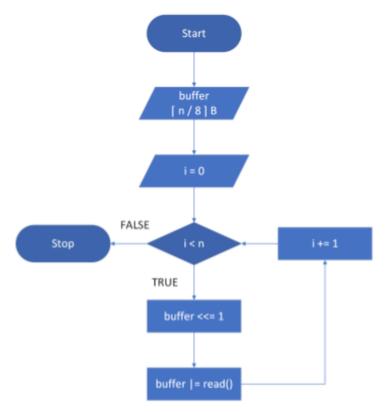

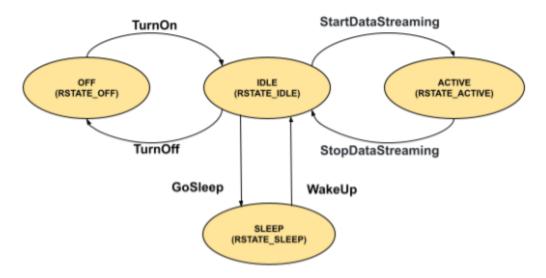

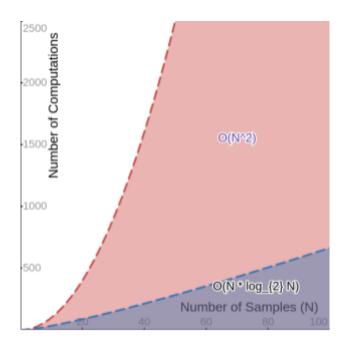

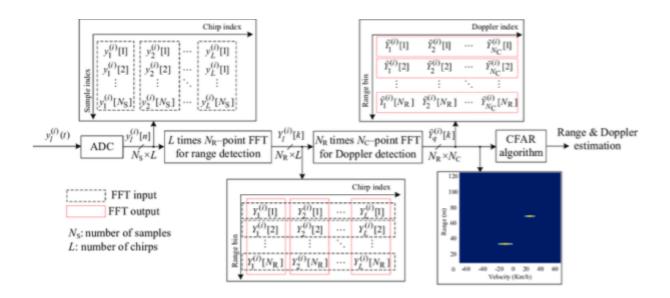

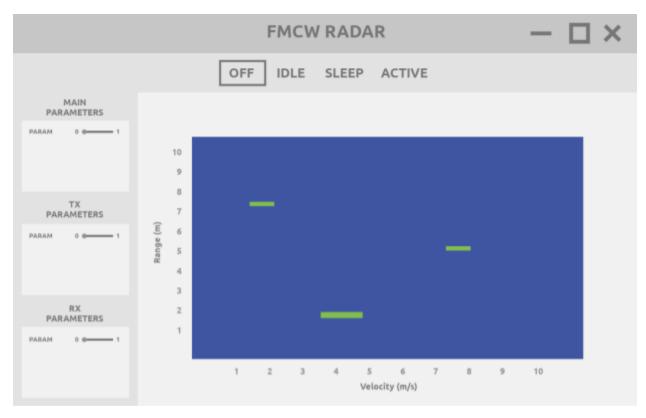

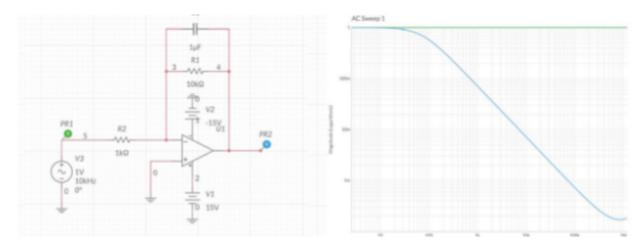

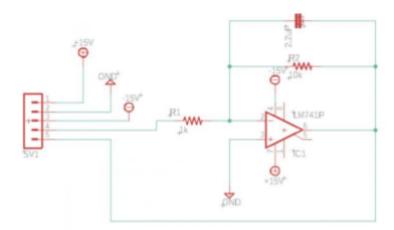

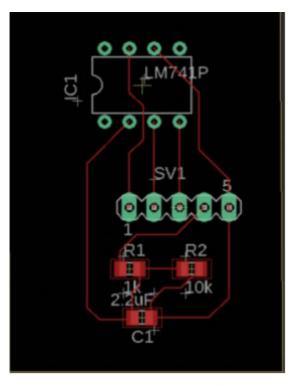

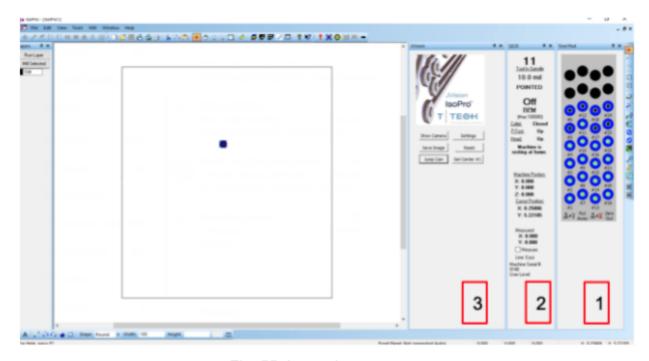

Fig. 19. LNA Topologies