Senior Design I Documentation EEL4914 – Dr. Samuel Richie and Dr. Lei Wei December 10th, 2015

> Group 31 Stephen Williams – BSEE Kenneth Richardson – BSCpE John Shepherd – BSEE Gilson Rodrigues – BSEE

| 1. Executive Summary                                  | . 1 |

|-------------------------------------------------------|-----|

| 2. Project Definition                                 | . 2 |

| 2.1 Project Motivation                                | . 3 |

| 2.2 Objectives and Goals                              | . 3 |

| 2.3 Requirements Specification                        | . 3 |

| 3. Relevant Research                                  | . 4 |

| 3.1 Similar Past Products                             | . 4 |

| 3.1.1 Transcoders                                     | . 5 |

| 3.1.2 Line Doublers                                   | . 6 |

| 3.1.3 Full Scalers                                    | . 8 |

| 3.2 Relevant Standards                                | . 9 |

| 3.3 Realistic Design Constraints                      |     |

| 3.4 Technologies                                      | 15  |

| 3.4.1 Data Signals                                    |     |

| 3.4.1.1 Analog Video                                  | 15  |

| 3.4.1.1.1 Analog Synchronization Signaling            | 17  |

| 3.4.1.2 Analog Audio                                  | 19  |

| 3.4.1.3 Digital Audio                                 | 19  |

| 3.4.1.4 Digital Video                                 | 20  |

| 3.4.1.5 HDMI                                          | 21  |

| 3.4.2 Communications                                  | 23  |

| 3.4.2.1 I <sup>2</sup> C (Inter-Integrated Circuit)   | 24  |

| 3.4.2.2 Serial Peripheral Interface (SPI)             | 25  |

| 3.4.2.3 UART (Universal Asynch. Receiver/Transmitter) | 26  |

| 3.4.3 FPGA                                            | 27  |

| 3.4.3.1 Xilinx Spartan-3 Family                       | 27  |

| 3.4.3.2 Xilinx Spartan-6 Family                       | 28  |

| 3.4.3.3 Xilinx Artix-7 Family                         | 28  |

| 3.4.4 Microcontrollers                                | 30  |

| 3.4.4.1 Texas Instruments MSP430G2553                 | 30  |

| 3.4.4.2 Texas Instruments TM4C123GH6PM                | 31  |

| 3.4.4.3 STMicroelectronics STM32F0 Line               | 31  |

| 3.4.4.4 STMicroelectronics STM32F103RBT6              | 32  |

| 3.4.4.5 Summary and Selection                         | 33  |

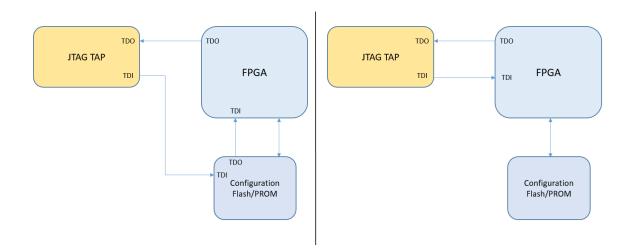

| 3.4.5 In-System Programming                |    |

|--------------------------------------------|----|

| 3.4.5.1 FPGA JTAG Programming              |    |

| 3.4.5.2 Microcontroller                    |    |

| 3.4.5.2.1 Serial Wire Debug and ST-LINK/V2 |    |

| 3.4.5.2.2 STMicroelectronics Bootloader    |    |

| 3.4.6 USB Interface                        |    |

| 3.4.6.1 Bootloader                         |    |

| 3.4.6.2 FTDI FT232                         |    |

| 3.4.7 SD Cards                             |    |

| 3.4.8 Supported Connectors                 |    |

| 3.4.8.1 SCART                              |    |

| 3.4.8.2 Component                          |    |

| 3.4.8.3 VGA                                |    |

| 3.4.8.4 HDMI                               |    |

| 3.4.8.5 Stereo Audio                       |    |

| 3.4.9 Video Decoder                        |    |

| 3.4.10 Audio Decoder                       |    |

| 3.4.11 HDMI Transmitter/Encoder            | 47 |

| 3.4.12 VGA Output Support                  |    |

| 3.4.13 LEDs                                | 49 |

| 3.4.14 Remote Control                      | 50 |

| 3.4.14.1 Bluetooth                         |    |

| 3.4.14.2 Infrared                          | 52 |

| 3.4.15 Power                               | 55 |

| 3.4.15.1 Power Requirements                | 55 |

| 3.4.15.2 Regulators and Sequencers         | 57 |

| 4. Design                                  |    |

| 4.1 Hardware                               | 63 |

| 4.1.1 Video Decoding Subsystem             | 63 |

| 4.1.2 Audio Decoding Subsystem             | 64 |

| 4.1.3 HDMI Encoding Subsystem              | 65 |

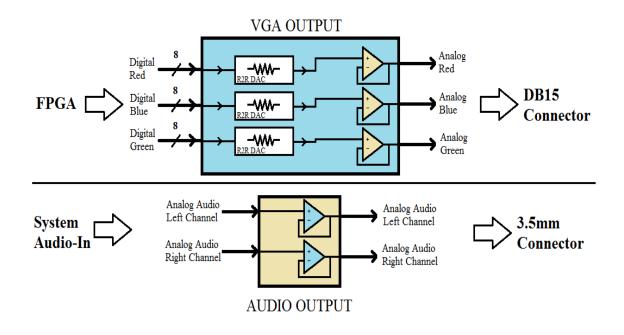

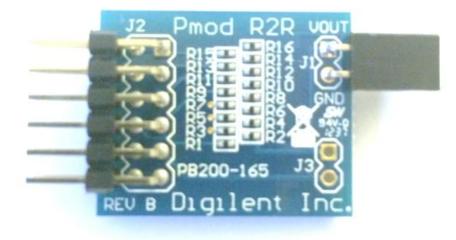

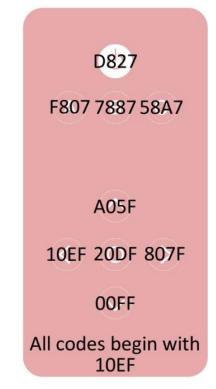

| 4.1.4 VGA Output Stage                     | 67 |

| 4.1.5 Remote Control Subsystem             | 69 |

| 4.1.6 LED Indicators Subsystem             |    |

| 4.1.7 Subsystems Interfacing                      |    |

|---------------------------------------------------|----|

| 4.1.7.1 Microcontroller Interface                 | 71 |

| 4.1.8 Power Distribution System                   |    |

| 4.1.8.1 Power Rails                               |    |

| 4.1.8.2 FPGA                                      |    |

| 4.1.8.3 MCU                                       |    |

| 4.1.8.4 Video Decoder                             | 86 |

| 4.1.8.5 Audio ADC                                 |    |

| 4.1.8.5. USB UART IC                              |    |

| 4.1.8.7 Infrared Receiver                         |    |

| 4.8.1.8 Shift Registers                           |    |

| 4.1.8.9 Video Buffer                              |    |

| 4.1.8.10 Amplifiers                               |    |

| 4.1.8.11 Power Sequencer                          |    |

| 4.2 Software                                      |    |

| 4.2.1 FPGA                                        |    |

| 4.2.1.1 Logic                                     |    |

| 4.2.1.1.1 Image Scaler                            |    |

| 4.2.1.2 Interfaces                                |    |

| 4.2.1.2.1 Microcontroller Interface               |    |

| 4.2.1.2.2 Audio/Video Pipeline Interfaces         |    |

| 4.1.2.3 GUI GENERATOR                             |    |

| 4.2.2 Microcontroller                             |    |

| 4.2.2.1 Logical Interface Description             |    |

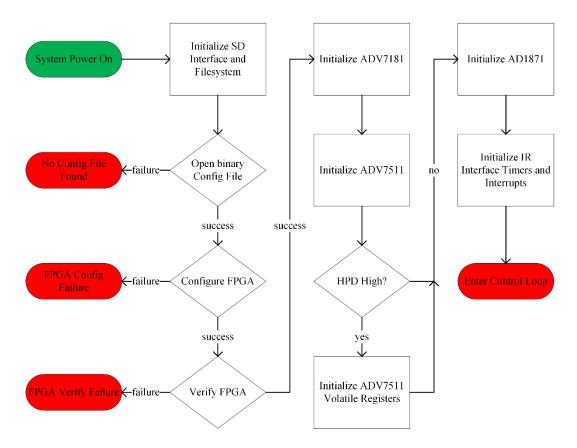

| 4.2.2.2 Initialization Logic                      |    |

| 4.2.2.2.1 FPGA Post-programming Initialization    |    |

| 4.2.2.2.2 Special-Purpose IC Initialization       |    |

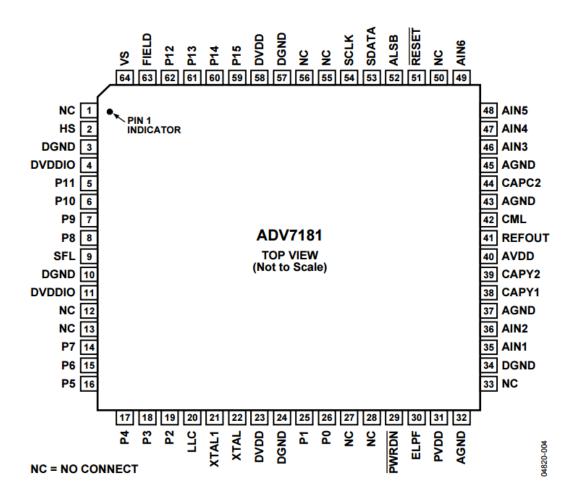

| 4.2.2.2.1 ADV7181 and ADV7511                     |    |

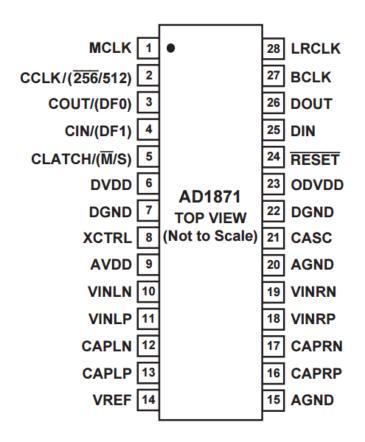

| 4.2.2.2.2 AD1871                                  |    |

| 4.2.2.2.3 IR Interface Timer Clock Initialization |    |

| 4.2.2.2.4 Initialization Routines Summary         |    |

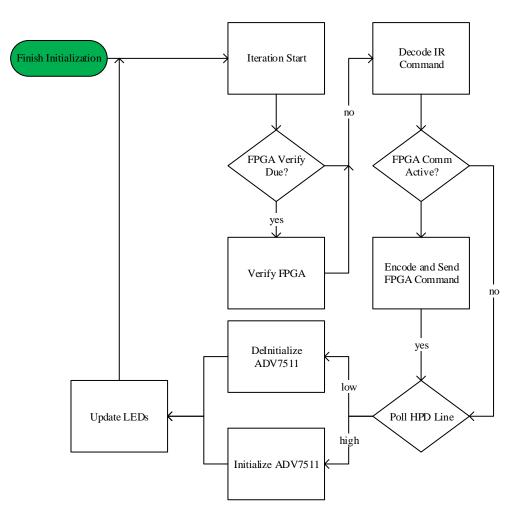

| 4.2.2.3 Control Logic                             |    |

| 4.2.2.3.1 IR Decoding                             |    |

| 4.2.2.3.2 FPGA Verification and Signaling         |    |

| 4.2.2.3.3 HDMI Transmitter Control          | 108 |

|---------------------------------------------|-----|

| 4.2.2.3.4 LED Control                       | 108 |

| 4.2.2.3.5 Control Routines Summary          | 109 |

| 4.2.2.3.6 Summary                           | 109 |

| 4.2.3 In-System Programming                 | 110 |

| 4.2.3.1 Microcontroller Reprogramming       | 110 |

| 4.2.3.2 FPGA Reprogramming                  | 110 |

| 4.2.3.2.1 SD Card Interface                 | 110 |

| 4.2.3.2.2 FPGA Slave Serial Configuration   | 111 |

| 5. Design Summary                           | 113 |

| 5.1 Hardware Design Summary                 | 113 |

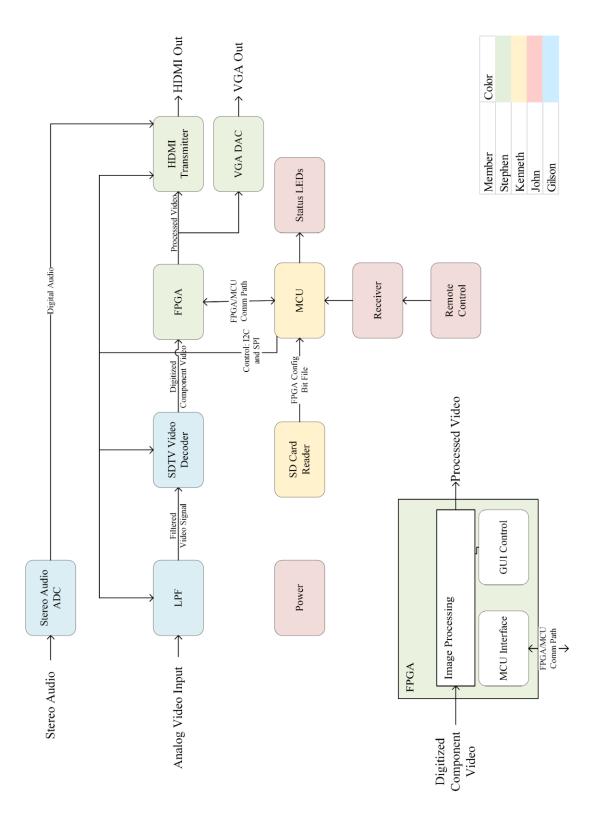

| 5.1.1 System Block Diagram                  | 113 |

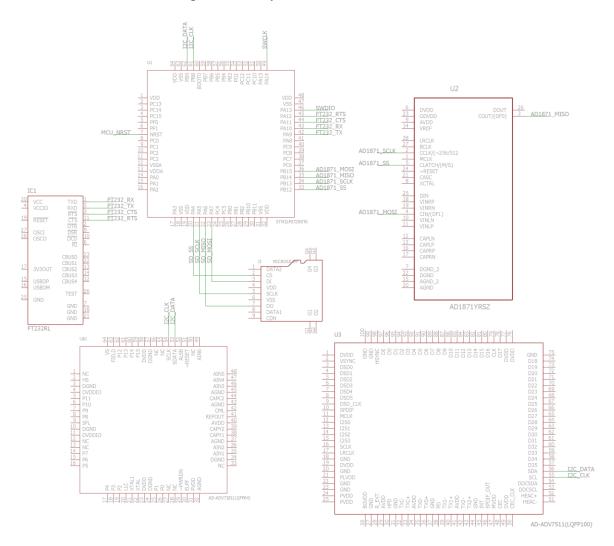

| 5.1.2 Microcontroller Interface Connections | 115 |

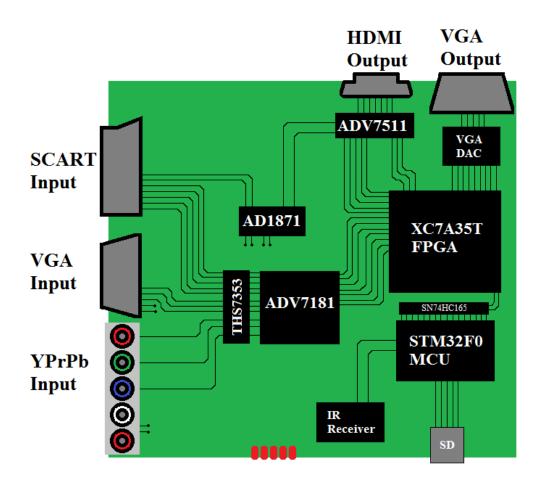

| 5.1.3 PCB Mockup                            | 116 |

| 5.2 Software Block Diagrams and Summary     | 117 |

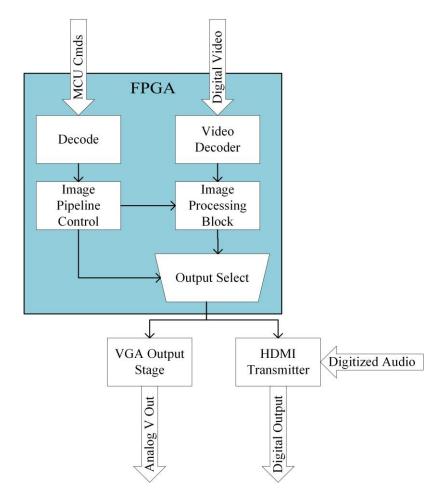

| 5.2.1 FPGA Logic Summary                    | 117 |

| 5.2.2 Microcontroller Logic and Flowcharts  | 117 |

| 5.2.2.1 Initialization                      | 117 |

| 5.2.2.2 Control                             |     |

| 6. Construction                             | 119 |

| 6.1 Hardware                                | 119 |

| 6.1.1 Acquisition                           | 119 |

| 6.2 PCB Fabrication and Population          | 120 |

| 6.3 Software Tools                          | 120 |

| 6.3.1 IDEs and Development Tools            | 120 |

| 6.3.2 Programmers and Flashing Utilities    | 120 |

| 6.3.3 Software Libraries and Sources        | 121 |

| 7. Prototype Testing                        | 121 |

| 7.1 Microcontroller Interface Testing       | 121 |

| 7.1.1 Analog Devices IC Configuration       | 122 |

| 7.1.2 ADV7511 HPD Dependent Control         | 122 |

| 7.1.3 SD Interface                          |     |

| 7.1.4 FPGA Programming and Interface        | 122 |

| 7.1.5 IR Decoding                           | 123 |

| 7.2 Target Companion Devices                |     |

|---------------------------------------------|-----|

| 7.3 Requirements Specification Verification |     |

| 8. Administrative                           |     |

| 8.1 Budget                                  |     |

| 8.2 Milestones                              | 125 |

| 8.3 Division of Labor                       |     |

| 8.4 Decision Making                         |     |

| 8.5 Meeting Structure                       |     |

| 8.6 Communication and Remote Collaboration  |     |

| Appendix A. Copyright Permissions           |     |

|                                             |     |

# 1. Executive Summary

With the move from analog video signals and CRT television sets to an all-digital world of flat panel LCD, plasma, and other technologies, many older entertainment peripherals yield inadequate results when displayed on these new sets. The reasons for this are numerous. Television manufacturers ultimately make the decision which additional conversion and scaling techniques they would like to implement into the set itself. With the television industry as competitive as ever, the additional cost of considering specific devices and edge cases for a consumer base, overwhelmingly using newer digital devices, could make a large impact on units sold.

For many manufacturers, the solution is to provide the bare minimum in analog device support and connector compatibility. Often the only analog connector provided is composite. Even when the connectors themselves are present, the methods used in processing and displaying them are typically applied in a broad and insufficient way. The result is an image which lacks clarity as seen in Figure 1.

Figure 1: 240p signal. TV default processing mode (left), XRGB-mini device output (right).

This project is focused specifically on providing an intermediary device between classic 8bit/16-bit videogame consoles and modern television sets similar to Micomsoft's XRGBmini, but at a lower cost and with a more focused feature set. These videogame systems typically output a 240p (320x240) signal over one of the aforementioned analog connections. Modern televisions often handle such 240p signals poorly, interpreting the signals as 480i (640x480 interlaced) and inappropriately applying de-interlacing techniques to a progressive scan signal.

## 2. Project Definition

We plan to solve several of these issues with a single device. Our device exists between the videogame console and the modern television. With a 240p analog input, our device will properly scale the signal to 480p through a process known as line-doubling using an FPGA and accompanying filter and conversion circuitry. Line-doubling scales the resolution by a factor of two while requiring very little processing time. While modern televisions often have trouble with 240p signals, the majority today handle 480p signals well enough for the average user. Our goal is to bridge this gap between troublesome 240p and well-handled 480p for any television set. If desired, the console stereo audio output may also be provided as input and carried over HDMI to the display for a single, convenient connection point.

Figure 2: 240p signal displayed on a CRT television with darkened scanlines (left), emulated scanlines via XRGB-mini.

In addition to scaling and converting the image, our device provides darkened scanline emulation. A darkened scanline, in the context of 240p displayed on a CRT television, refers to the darkening of every odd line due to only one of the image fields being transmitted as shown in Figure 2. These darkened scanlines are absent when a 240p signal is displayed on a digital television. This device will allow the user to darken every other picture line, providing a classic visual effect. An on-screen overlay will allow the user to simply and quickly check the device status and operating mode for making desired adjustments. This overlay will be interfaced with via remote control, allowing the user to adjust various image properties in addition to scanline control.

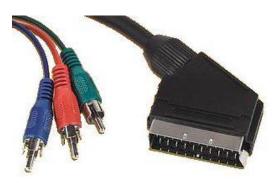

On the strict hardware interface side, our device will support a variety of analog video inputs. It will support component-YPbPr video, 15-pin VGA-RGBHV, and SCART-RGBS. For output, the device will support digital output via HDMI. This collection of

input connections covers nearly all common connections seen on the videogame consoles targeted for use with this device.

# 2.1 Project Motivation

We decided to design a video scaler because of our dissatisfaction with modern television 240p video support. Existing devices are either too expensive, or have poor performance. There exists a gap of suitable video processing products in the \$150-\$250 price range; we decided to seize the opportunity and create such a device. FPGAs are excellent for image processing and provide the designer with fine-grain control of computation resources. This allows us to create a custom video processing data path which performs extremely well with 240p video content.

# 2.2 Objectives and Goals

Our goal is to design a video processing device geared towards 240p video content. We plan to achieve this goal while also producing a device that is cost competitive in the current market. It must provide fine control over settings which impact image quality such as scaling factor and color levels. In order to preserve part of the experience of playing on a CRT television our device will have the ability to add in darkened scanlines to the image, rounded frame corners, and some non-linear lighting effects to mimic the characteristics of CRT display technology.

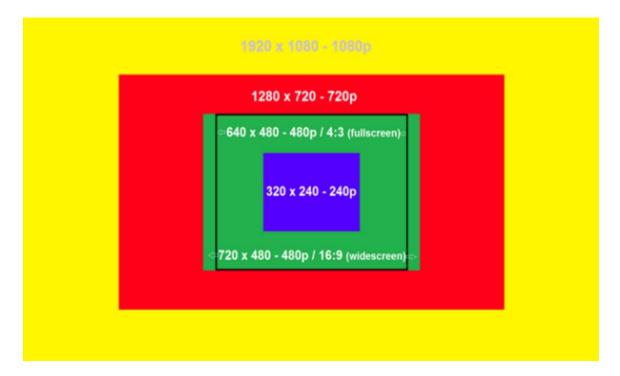

Image quality is largely determined by resolution and color balance. It is therefore important that our device has the ability to adjust such settings in order to produce a picture which is pleasing to the eye. The resolution will be controlled by an integer scaling factor, if the input resolution is 240p (320x240) with a scaling factor of two, then the scaled resolution is 480p (640x480). The user will be able to adjust the individual color channels in the RGB signals to a level which they personally find appealing.

While modern digital televisions are desired for their high resolution and crisp image, there is a certain nostalgia associated with the quirks of CRT display technology. When displaying 240p content, CRT televisions would have darken every other scanline; the darkened scanline effect is referred to as "scanlines" in the video game community. These scanlines and other mimicking techniques all work together to give the user an experience which merges together the benefits of modern and vintage television sets.

In order for the Super Doubler to be competitive it must provide flexible high performance video processing at a reasonable cost with an easy to use interface.

# 2.3 Requirements Specification

Requirements were developed at the outset of the project and refined over the course of preparing this design document along the lines of 6 key areas: physical characteristics, power consumption, device input/output connector and format support, technical

characteristics, cost, and user experience. The requirements are summarized in the list below.

|                                                                  | Weight < 2 lbs                                           |  |  |

|------------------------------------------------------------------|----------------------------------------------------------|--|--|

| Physical                                                         | Volume $< 25 \text{ in}^3$                               |  |  |

|                                                                  | Complete standalone device in single enclosure           |  |  |

| Power                                                            | Total device power usage $< 20$ watts                    |  |  |

|                                                                  | Support component-YPbPr, VGA-RGBHV, and SCART-RGBS       |  |  |

| I/O Support                                                      | Support LR stereo audio input                            |  |  |

| I/O Support                                                      | Support HDMI output                                      |  |  |

|                                                                  | Support VGA output                                       |  |  |

|                                                                  | Processing time < 30 ms                                  |  |  |

| Technical                                                        | Full 4:4:4 RGB Processing                                |  |  |

| Technical                                                        | Resolution Scale Factor $\geq 2$                         |  |  |

|                                                                  | $240p \Leftrightarrow 480i$ switch time < 2 frames' time |  |  |

| Cost                                                             | Device bill of materials < \$150                         |  |  |

|                                                                  | Support overlay for inspecting device statu              |  |  |

| User                                                             | Support for scanline emulation                           |  |  |

| <b>Experience</b> Support for configuration using remote control |                                                          |  |  |

|                                                                  | Support for FPGA reconfiguration via SD Card             |  |  |

Table 1: Summary of requirements specification for the project.

These requirements are developed to facilitate specific design strategies and will be used to judge prototypes and proposed designs. Adherence to these requirements should remain absolutely critical to every decision made in the design process.

# 3. Relevant Research

# 3.1 Similar Past Products

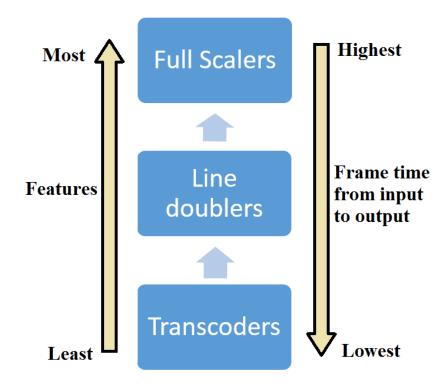

For as long as digital television sets have been on the market, there has been a need to support devices which output analog video signals. Video formats such as composite, s-video, component, and SCART are used by classic video game consoles. While it is possible to find current TV models which support some of these format, many of them do not properly support 240p video signals. There are many existing devices which aim to improve 240p analog video support with digital TV sets. The capabilities of these devices vary greatly with some only providing very simple color space conversion, such devices are called transcoders. More capable devices provide resolution scaling, such devices are called line doublers when performing 2x scaling and full scalers otherwise. We will limit our discussion to products which are intended to be used with video game consoles as other devices provide poor results. The hierarchy shown in Figure 3 will be used to classify previous devices based on a minimum feature set. From least capable to most capable it is: transcoders, line doublers, and full scalers.

Figure 3: A line doubler represents a balance between processing time a features.

#### 3.1.1 Transcoders

Older 240p capable video-game consoles have the ability to use RGB video. RGB video is typically transmitted using a SCART cable and is considered the best option for 240p consoles. Unfortunately the SCART video standard did not catch on in North America, with many US companies opting to support component video or s-video instead. RGB to YUV transcoders represent a low-cost solution to support your older video game consoles with a digital TV set. These devices perform a simple color-space conversion from the RGB color-space to the digital component (YUV/YC<sub>R</sub>C<sub>B</sub>) color-space. In addition to RGB to YUV transcoders, there are also YUV to VGA transcoders and many other types.

Transcoding devices fall into two sub-categories, those with no scaling and those which scale the input to 480p. Units which provide no scaling face the issue of the digital TV not supporting the low resolution of 240p, even if it is in the correct color space. These devices are low-cost products from China and have many different names despite being the same exact product. An ebay search of "SCART to YUV transcoders" yields many product results. SCART to YUV transcoders are typically used to provide RGB support on a CRT monitor which only supports YUV. For reference, a pure transcoder is shown in Figure 4 below. These devices will receive little attention here given that they have such limited compatibility with digital TV sets, instead we will focus on devices which are supported by most digital TV sets.

Figure 4: RGB to YUV transcoder, courtesy of SPECIALTYAV.

Units which provide scaling in addition to transcoding usually support a maximum output resolution of 480p. This ensures compatibility with most digital TV sets. A few notable examples of such devices are the HDBox Pro and the Arcadeforge SLG IN A BOX. However, these units treat the 240p signal as a 480i signal; while transcoding is accomplished, the picture quality is ruined by the de-interlacing. Although the artifacts introduced by deinterlacing of 240p are undesirable, the ability to use RGB as the source video makes these devices considered worthwhile. This is because TVs apply deinterlacing to the composite video input, so regardless of whether you use these devices or not the video signal is being deinterlaced. Transcoders typically introduce a noticeable amount of latency to the video processing data path which is perceived as input lag by the user.

Given that transcoders usually occupy a lower price bracket than line doublers and full scalers, it makes sense to use them in certain situations. If you are playing a slower-paced game where user input timing is not as critical then processing latency is acceptable. If the device is intended to be a one-off solution to provide support for a single console, then the robust solution provided by a full scaler is not needed. Our project at the minimum will support signal transcoding in order to be compatible with all of the color-spaces used in older video game consoles.

## 3.1.2 Line Doublers

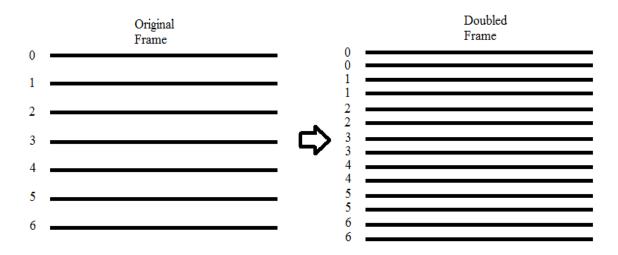

The next set of devices scales the input video signal in a way that is much more pleasing to the eye than the methods used by previously mentioned devices. This scaling method is called line doubling which essentially duplicates each line. Here the signal is treated properly as 240p and not 480i; therefore no deinterlacing is applied in either the TV's processing stage or the external device's processing stage. This method leads to an increase in sharpness and brightness, both of which are desirable for 240p console art styles. Such devices are referred to as line doublers. We include devices which are pure line doublers and devices which are full scalers with a line doubling mode.

Figure 5: Basic idea of line doubling.

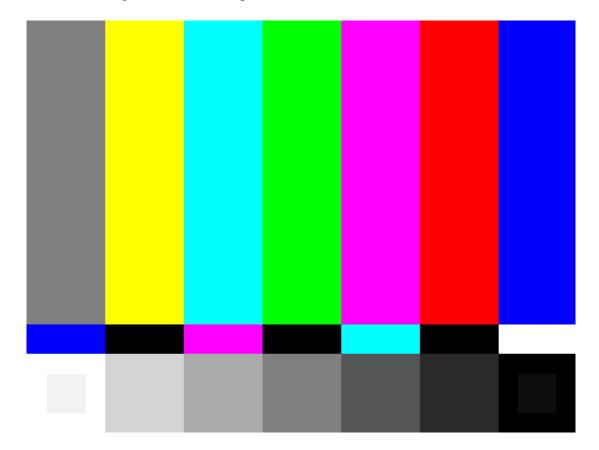

While digital TVs have trouble processing 240p video signals natively, most have little issues with the handling of 480p content. In certain situations a device which only performs a scaling of a factor of two can be ideal, such scaling can be done in a manner which introduces minimal input latency. However, if the TV has poor 480p handling then a full scaler may be necessary. Line doublers use a fast scaling method which is two-pronged, first horizontal scaling is performed with vertical scaling following. Horizontal scaling is accomplished by using an FPGA pixel clock which is twice the frequency input video signal's pixel clock, the pixel clock determines when to send a new pixel to screen. Since a picture is scanned to the screen in rows of pixels doubling of the pixel clock frequency doubles the pixel width of a picture row. To accomplish vertical scaling, each picture row is stored in a buffer and then when then each buffer is read twice to the screen. This double the height of the image by repeating every horizontal row twice. This scaling method requires very little processing time as the only active operation is the buffering of a single picture line. In comparison, other scaling methods rely on a partial to full frame buffer with costly multiply-accumulate operations to output the scaled frame.

Regarded as one of the best 240p line doublers on the market, Micomsoft's XRGB-3 is a full scaler with a special mode, B1, which lets it act as a pure line doubler. In this mode the XRGB-3 supports scaling of 240p to 480p with various analog video inputs from composite to scart. The XRGB-3 is able to provide near latency-free scaling by using a VGA output, no conversion to digital video is performed. This means you can use the XRGB-3 with a progressive scan CRT you can enjoy a full bright 480p image from a 240p console. However since the signal output is VGA, the user will still experience input latency as the XRGB-3's analog output is converted to a digital format by the TV. The XRGB-3 does not support 240p over component, only RGB, therefore a RGB to YUV transcoder is still needed for 240p component video support. This is only a slight issue as many video game consoles support both component and RGB video output.

Line doublers commonly support a feature known as scanline emulation. Scanline emulation darkens every other picture line in order to mimic the way a 240p video signal

is scanned to a CRT display. Scanline emulation is desired by many users of video scaling devices as it helps achieve an image that is similar to the classic experience of playing the video game on a CRT. Our device will at minimum support line doubling and color-space transcoding.

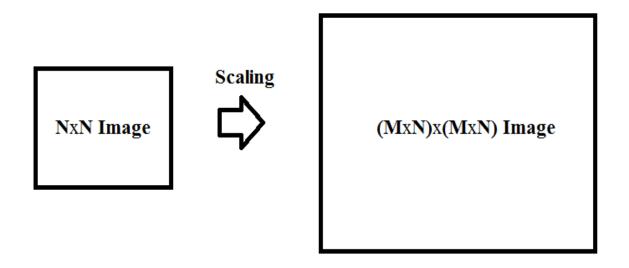

### 3.1.3 Full Scalers

Representing the peak class of devices in video processing devices for game consoles are full scalers. Full scalers are devices which can scale the input video resolution to an arbitrary output resolution, though realistically the output resolution is limited to what current TVs support. Here we will consider devices which support an output of 480p, 720p, and 1080p. Image scaling in such devices in accomplished through various scaling algorithms, manufacturers do not often disclose their algorithm, leaving it to the users to determine by inspection the algorithm used. Typically an ASIC is used as the primary scaling hardware, though FPGAs have started to appear with increased frequency lately.

Figure 6: Flexibility provided by full scalers allows the user to choose an arbitrary output resolution within device limitations.

The previously mentioned XRGB-3 features a full scaler mode in addition to its line doubling mode. The XRGB-3 supports output resolutions up to 1080p although its scaling method requires fine-tuning and adds more input latency than other devices. The current best-in-class device is another product from Micomsoft's lineup, the XRGB-mini Framemeister. At the price of \$350 the XRGB-mini does not come cheap. The Framemeister supports emulated scanlines, 1080p, and many other image adjustment options. As far as video inputs, the Framemeister supports component, composite, s-video, HDMI, and SCART. The Framemeister is very competitive in regards to input latency, with an added delay of only 28ms. Unfortunately all scaling is done by the Framemeister's full scaling chip with no option to enter a dedicated line double mode. This means that even if the user only needs 2x scaling, which should incur minimal delay, the signal still has to spend 28ms being processing in full scaling mode.

Our device sits roughly in-between the line doubling and full scaler classes of device. It will support multiple analog video formats at 240p as input with a maximum output of 720p. Our device will include a dedicated low-latency line doubling mode in addition to emulated scanlines. It is therefore fitting that our device be known as the "Super Doubler".

#### 3.2 Relevant Standards

Television is technically defined as the conversion of light to electrical energy in order to share information. With a variety of electronic video equipment involved in this process, standards and protocols had to be developed in order to monitor how this information was being created and exchanged and to ensure consistency. The justification for our project design plays off of the existing disparity in picture quality when modern digital televisions are interfaced with retro peripherals, such as Nintendo, Genesis (Sega) and PlayStation. When these older entertainment consoles were first created, they were designed to be compatible with analog televisions and output at 240p. When the digital LCD and plasma televisions were designed, they did not yield quality images or performance when run with the older consoles. This dissemblance is largely due to standards set up by the committees under the umbrella organization ISO, or International Organization of Standards. The ISO is a worldwide organization consisting of over 100 countries that moderates technical standards for science, technology and economic measures. There are many organizations around the world that fall under the ISO that regulate video including the National Television System Committee (NTSC), The Advanced Television Systems Committee standards (ATSC), Sequential Color with Memory (SECAM), and Phase Alternating Line PAL/SCAM.

The NTSC, used mostly in North America, was first created in the 1940's to set forth the minimal requirements for analog video in black and white. When color television was created, in 1953 the NTSC revitalized the original standards for analog video to include color information; referred to Conventional Definition Television (CDTV). These standards were continued up until 2010 when digital video began to become more popular and analog transmitters were forced to shut down. The ATSC was started in the 1980s when the digital video first came about and revitalized the outdated analog video protocols to create criteria standards for digital video, including SDTV, EDTV, and HDTV. Whether referring to digital or analog video standards, several components are referenced such as image resolution, aspect ratio, pixel aspect ratio, scanning process, audio frequency and frame rate.

| CDTV Standards | Pixel/line | Aspect Ratio | Line Count | Frame Rate | Scan Mode |

|----------------|------------|--------------|------------|------------|-----------|

| NTSC           | 640        | 4X3          | 480        | 29.97      | Interlace |

| PAL            | 760        | 4X3          | 580        | 25         | Interlace |

| SECAM          | 760        | 4X3          | 580        | 25         | Interlace |

Table 2: CDTV standards.

| Resolution |                  | Aspect<br>Ratio | Pixel aspect<br>ratio                | Scanning    | Frame rate (Hz)      |

|------------|------------------|-----------------|--------------------------------------|-------------|----------------------|

| Vertical   | tical Horizontal |                 |                                      |             |                      |

| 1080       | 1920             | 16:09           | 1:01                                 | Progressive | 24<br>30<br>25       |

|            |                  |                 |                                      | Progressive | 60<br>50             |

|            |                  |                 |                                      | Interlaced  | 29.97<br>30<br>25    |

| 1080       | 1440             | 16:09           | HDV<br>(4:3)                         | Progressive | 24<br>30<br>25       |

|            |                  |                 |                                      | Progressive | 60<br>50             |

|            |                  |                 |                                      | Interlaced  | 29.97<br>30<br>25    |

| 720        | 1280             | 16:09           | 1:01                                 | Progressive | 24<br>30<br>60<br>50 |

| 480        | 720              | 4:3 or 16:9     | SMPTE<br>259M<br>(10:11 OR<br>40:30) | Progressive | 24<br>30<br>60<br>50 |

|            |                  |                 |                                      | Interlaced  | 29.97<br>30<br>25    |

| 480        | 640              | 4:03            | 1:01                                 | Progressive | 24<br>30<br>60<br>50 |

|            |                  |                 |                                      | Interlaced  | 29.97<br>30<br>25    |

| 480        | 528              | 4:03            | (40:33)                              | Progressive | 25                   |

|            |                  |                 |                                      | Interlaced  | 29.97<br>25          |

| 240        | 352              | 4:03            | (10:11)                              | Progressive | 25                   |

Table 3: ATSC Digital video standards.

Image resolution refers to the quality of the video image, which is controlled by the number of pixels in a horizontal scan line multiplied by the number of scan lines in a frame. The resolution of a picture refers to how close the horizontal lines can be to each other and still be visible. The relevant standard for analog NTSC video was 480 horizontal lines comprised of 640 pixels per line. This gives us the spatial density resolution, or the number of pixels that make up one frame and it is usually denoted by (640X480). The ATSC standard for digital video was increased to 720X486. When the number of pixels is increased the image becomes more detailed. The higher the resolution of an image the crisper the image and can be displayed on a larger screen while maintaining the integrity of image.

The next standard is the pixel aspect ratio, which refers to the size and shape of the individual pixel. When original analog systems were set to become digitalized, the number of scan lines could not be changed due to the original standards set forth by the National Television System Committee (NTSC). In order to change the pixel aspect ratio, the number of pixels per scan line where increased which changed the shape of the pixels to a narrow, vertical and rectangular shape. The amount of pixels within an image directly correlates to the amount of information within that image. When you increase the number of pixels per line you add to the image resolution. Current digital standards for a 480p system are 4X3 or 1.33X1 ratio. This poses a problem when running a 240p program or game that uses the original standards set forth by the NTSC at a pixel ratio of 0.91:1; creating a disparity in image resolution.

Scan modes is the next standard reviewed and there consists two different types. The first is interlace scanning, which splits each frame of a video into two fields which in turn can increase the frame rate of the video image without increasing the bandwidth. One of the fields contains the odd lines of information and the other contains the even lines. When the video is played the two fields are "interlaced" together to form one frame. The result of this type of scanning produces a better quality image and reduces the "flicker" of the image. The benefit of this type of scanning is that it reduces cost but decreasing the amount of bandwidth. In addition, this scan mode provides a higher refresh rate which makes objects that are in motion in the image appear more smooth. With progressively scanned images, the frame is not split and instead is scanned from top to bottom as well as each line in the frame is scanned and then reproduced as one frame. So essentially each line is redrawn in sequence. Modern digital televisions run on progressive scanning, hence the "p" in 480p. When a 240p video console is utilized, the current standard equipment on a modern television is not equipped to convert the 240p to 480p and usually incorrectly converts from progressive scanning to interlacing scanning which distorts the image and creates processing latency.

The final standard is the frame rate. The frame rate refers to the number of full frames that are scanned per second and basically determines the speed in which an image is scanned. The standard frame rate for a 480p can be 24, 30 or 60 frames per second. If the scan mode is progressive or interlaced, it will be denoted as a p or i behind the number. 24p and 30p are progressive formats that are used mostly in translating a video signal to film where as 60p is utilized frequently with HDTV. For the analog video the standard is 29.97 fps.

As you can see, these standards set forth for both analog and digital video contribute to difficulties with connecting older entertainment peripherals to newer digital technology. When using a 240p retro video game console that originally processes analog signal, with a HDTV that may lack analog inputs can distort the image and create lag time when trying to play the older games. The video conversion device that we have designed will be an intermediary between the two systems, almost like a bridge, that with convert the analog to HMDI and at the same time upscale the video resolution allowing the user to play older games with a newer television.

Figure 7: Video screen size in relation to resolution. Courtesy of RetroRGB.com.

## 3.3 Realistic Design Constraints

There can be several constraints that are intrinsic to any product design including economic, social, manufacturability and sustainability. These restrictions or hindrances can be roadblocks to design and development of a product or can spur creative problem solving that guides the conceptualization of a new and unique product. At this point in our project it is difficult to ascertain all design constraints as the prototype has not yet been completed but being proactive in identifying obvious constraints will help to avoid problems during the next phase of the project. Within this section of the paper we will discuss the impact of certain constraints on the video industry itself and how that guided our decision making for the design of our video conversion unit, The Super-Doubler.

What we propose to do with our video conversion unit is to create an intermediary device between classic 8-16 bit analog video game consoles and modern digital televisions. This device will allow for a high resolution image with little to no lag time as well as provide the capabilities for the player to adjust image properties and control scan lines with a simple device that is also more cost effective compared to similar products on the market today.

The health and safety of the consumer utilizing our product is of the upmost concern and is a key factor when determining the design of our system. In this day an age where litigation is very common, it is important that all foreseeable hazards be eliminated and the consumer notified of potential harm regarding certain aspects of design than cannot be mitigated.

The main concern in regards to the health and safety of the consumer is a responsible and respectful utilization of electrical components. Our device requires the consumer to have to connect several connectors to electrical devices such the TV, video game console and the Super-Doubler. Incorrect connections or removing connections when the device is on can potentially result in harm to the user or the machinery. Our responsibility resides in a component design that limits the consumer exposure to electrical shock and providing disclaimers to the consumer regarding potential harm from the misuse of the device and its components and connections. As with an electrical device, caution should always be exercised. In addition, many times devices can heat up quickly when on. In regards to design, we would research and choose a component shell and insulation to limit overheating as well as provide clear communication to the consumer regarding heating up the device and its hardware.

A second aspect in regards to health and safety is the safety of children who may use this device or who may come in contact with the small pieces and cords that can present a choking hazard. Ensuring that our product utilizes tight locking connections and smaller cord lengths and limiting small removable hardware will limit this constraint however as with other safety hazards, it is important to communicate with the consumer the potential harm and to strongly recommend that it be kept out of reach of small children.

In addition to health and safety constraints there are also environmental constraints to be considered into the design of our product. Out product include microchips and electrical circuitry that functional optimally under certain temperatures and environments. In the structure if our device, it will be imperative to creative a tight locking seal to prevent moisture and dust from entering and corrupting the computer and electrical components. In addition, it will be important to communicate optimal temperature ranges to the consumer based off of the data sheet information for the microchips and other hardware to the consumer. Extreme heat and cold temperatures are to be avoided.

The next constraint to be considered is cost effectiveness. Currently, with the high competitive environment, most manufacturers of modern digital televisions and HDTVs outfit their products with the bare minimum requirements for analog connectors and support, which often turns out to be composite, in order to save money. With the change in the standards from analog video (NTSC) to digital (ATSC), AV equipment that utilizes the outdated analog signal is becoming obsolete. It is the bottom line that drives most developers in the video industry to provide top of the line technology with competitive pricing that yields a profit and yet costs minimal to manufacture. Products on the market today that claim similar results to our product design are pricy and can cost the consumer upward of \$400 for a video conversion unit to play their classic video games. These expensive alternatives do not afford the gamer the capabilities to adjust the image for the classic video game image and effect. The design of our product would have a large impact on the economics of the video industry. With an affordable conversion unit on the market, television manufacturers would not be forced to add additional and often costly additions to current models to reach the retro gamer consumer base, thus affecting the amount of units sold.

A cost effective design is what drove some of the decisions that we made in regards to product design in order to decrease the cost responsible for by the consumer. Even the best ideas can come to a stop if they become difficult or costly to manufacture or mass-produce. This is a vital component to the marketing value of our device. There are other devices out there that are similar and can recreate similar effects to our product design. The mark that sets our product above the others is that not only is it cost effective for the consumer but it is also simple and relatively cheap to manufacture. Initial budget estimate can be seen earlier in this document for a more detailed outlook. One of the difficulties approached by the group is that parts for our device are often sold in bulk. While this is a plus when mass producing technology equipment, as buying in bulk is normally cheaper, it created a higher than expected initial cost. One factor we took into consideration is the option to have more components than we need when creating our prototype in order to account for part failure as well as the ability to create multiple prototypes if desired. Ultimately our ambition is to cut back on cost once the prototype has been created and the necessary parts are identified. By utilizing bulk buying for hardware pieces as well as simplifying the design will allow us to create an effective product that will not put a financial strain on manufacturers and the consumer and allow us to be competitive with current technologies.

Another design constraint is the sustainability of our product. As technology continues to advance, older peripheral technologies become obsolete, as they are often unusable as video standards continue to change. With the design of our device, older technologies would be more sustainable over time as they would be able to connect with current and even newer technologies with small adjustments made. This also lends to the sustainability of the video conversion unit we are creating, as there will always be a need for a device that bridges the old with the new. Video gaming is a social phenomenon that has shown recent upward trends in popularity. Current statistics report an increase in the number of people playing video games. At present the largest portion of gamers are in the age group 36 years and up at 36%. Within that group, 25% are older than 50. There is a rise in gaming in the older age range, which first started gaming with classic consoles such as NES and SEGA. This is a large consumer base, that could be targeted and would benefit from an affordable and dynamic video game conversion unit, such as the one we are creating.

Identified above are the realistic design constraints that we have faced thus far in our project and of which have influenced our decision making process in regards to the procedures and architecture of our product. Undoubtedly, as we progress further into the design and actual prototype development of our conversion unit, more design constraints may become apparent and will need to be addressed.

## 3.4 Technologies

In this section we will discuss the technologies and components of video and audio that are relative to our prototype including: relevant research and impact on design, pros and cons of specific devices and components, and rational behind our design decisions in regards to specific hardware chosen.

## 3.4.1 Data Signals

The higher density of pixels allows HDTVs to display a more detailed picture, but should you use one of your favorite retro video game, for instance the super Nintendo, which outputs right about 57,344 pixels, you would soon realize that either the TV is not working properly or the video game resolution image needs drastic improvement and upscaling. Adopting newer technology usually means that you either have to give up on your older video games or settle for a subpar image with associated lag time in performance. While some may be content with this outcome, there are many that require a better solution and this is where our proposed conversion device comes into play. Before specific design components can be discussed, there needs to be a general understanding of why there is a disparity between older analog video devices and the newer digital technologies. Both analog video and digital video and their components will be discussed in detail in this section of the paper.

## 3.4.1.1 Analog Video

Analog video is the first video recording method that stored red, blue and green color waves. Essentially an electrical signal was recorded on a magnetic tape (VHS) which may or may not be an exact replica of the original image. Analog video begins with the capture of the images by a camera. The camera scans the video lines one by one from top to bottom until the whole video field, in other words the whole view in which the camera is capturing the images, are processed. With analog video the number of lines are fixed and the amount of detail of an image is largely decided by the frequency response. The camera then re-

scans the lines again from top to bottom. To sync the two systems properly, the camera transmits extra sync pulses so that the TV set can synchronize at the same line, which is transmitted, and at the same field. If the sync pulses are not received properly by the TV set because the video signal is too weak, then the screen starts scrolling and flipping and you get a corrupted image. One of the drawbacks of analog video is that they are susceptible to corruption and breakdown as they are not protected as digital data is. Also analog video signals are subject to noise interference which can reduce the accuracy of the signal and the quality of the image. One of the perks of analog video is that it consumes less bandwidth but information is easily lost or distorted.

The higher density of pixels allows HDTVs to display a more detailed picture, but should you use one of your favorite retro video game, for instance the super Nintendo, which outputs right about 57,344 pixels, you would soon realize that either the TV is not working properly or the video game resolution image needs drastic improvement and upscaling. Adopting newer technology usually means that you either have to give up on your older video games or settle for a subpar image with associated lag time in performance. While some may be content with this outcome, there are many that require a better solution and this is where our proposed conversion device saves the day. Before specific design component can be discussed, there needs to be a general understanding of why there is a disparity between older analog video devices and the newer digital technologies. Below we will discuss different data signals.

The understanding of how analog video signal works is indeed fundamental to the end goal of our project as most of the project will be dealing with analog signals and the conversion of its signals so that the creation of the "bridge" between the "older technology" and newer one can be made possible end goal of high quality image output. There are several different standards used worldwide in relation to analog video including PAL (Phase Alternation by Line), NTSC (National Television System Committee) and SECAM (Systeme Electronique Couleur Avec Memoire); though PAL and NTSC are used most often. Below the basic concepts of analog video and its applications will be discussed.

Analog video in a nutshell begins with the capture of the images by a camera. The camera scans the video lines one by one from top to bottom until the whole video field, in other words the whole view in which the camera is capturing the images, are processed. The camera then re-scans the lines again from top to bottom. To sync the two systems properly, the camera transmits extra sync pulses so that the TV set can synchronize at the same line, which is transmitted, and at the same field. If the sync pulses are not received properly by the TV set because the video signal is too weak for example, the screen starts scrolling and flipping and you get a corrupted image.

## 3.4.1.1.1 Analog Synchronization Signaling

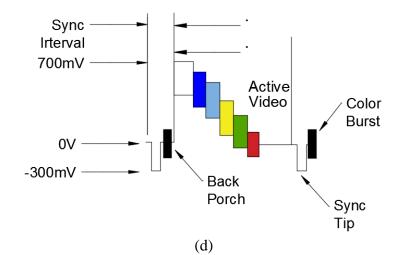

Analog video requires an extra signal at the end of each scan line and frame to ensure that when the video is transmitted it can be correctly refigured on the TV screen. Horizontal sync pulse separates the scan lines and denotes when a new line starts. Vertical sync is a longer pulse when compared to horizontal sync and indicates to the receiver when a new field is to be started.

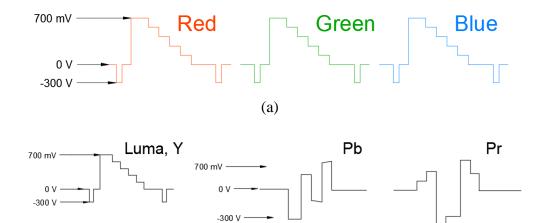

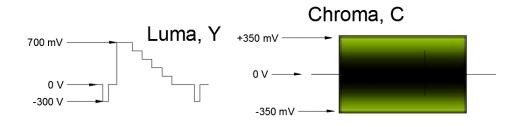

Component video synchronization may be sent in different ways since it requires an extra synchronization signal to be sent along with the video. There a several different types of sync including, separate sync, composite sync, sync-on-green, sync-on-luminance, and sync-on-composite. Separate sync uses two separate wires for horizontal and vertical synchronization and sends 5 different signals for red, green, blue and horizontal/vertical sync. Composite sync combines horizontal and vertical synchronization onto one pair of wires. Sync on green, combines composite sync with the green signal in RGB and only 3 signals are sent. Sync-on-luminance combines the luminance signal (Y) if the YPbPr system. Finally, sync-on-composite utilizes a composite video signal and combines it with RGB and utilizes the SCART connector. This type of sync is used mostly for devices that cannot process the RGB signals. The drawing below depicts the different synchronization signals for RGB, component, S-video and composite video.

Interestingly enough there are can also by sync issues between the audio and video signals during conversion creating a timing issue between the video and sound. This issue can result in lip syncing issues in which the image of a person talking does not line up with the speed of the sound. The standard sample rate for music is 44.1 kHz when coupled with anti-aliasing filters and converters. It was found that this lower sampling rate, compared to 48 kHz, was more beneficial in that it provided the same quality sound but also allowed for more music to be processed with fewer issues. The standard sampling rate for video was determined at 48 kHz which creates issues when utilized with the lower audio rate and mismatched sample rates can contribute to the lag between video and audio.

(b)

Figure 8: (a) RGB, (b) Component, (c) S-Video, (d) Composite video. Courtesy of maximintegrated.com.

#### 3.4.1.2 Analog Audio

There are two basic types of audio recordings; analog and digital. In this section we present the analog audio and why it will be mentioned is this part of the project and its contributing use. Analog audio was used exclusively in early years as the main processing system for sound until digital devices became the standard. Analog audio uses a method in which the analog signals are recorded and it reproduces an identical copy of the original sound waves. Among the disadvantages of analog signals, its drawbacks can affect the quality of the ending sound especially if what the application is to convert analog audio in digital audio. Analog audio signals are susceptible to noise and distortion due to the innate characteristics of electronic circuits and associated devices. In order to adjust the analog audio waves before its conversion we will be using a low pass filter in which it will be cleaning up analog signals before conversion and processing. The THS7353 low pass filter is a perfect choice for the application that it will be used since it is compatible with all video buffer applications; the THS7353 is a lower-power  $I^2C$  configurable which makes it flexible for the application that it will have to achieve, further details of the  $I^2C$  configurations will be discussed in a later section. Since the audio signal encompasses a much smaller range of spectrum space than video, audio recordings in analog are direct recordings. To conclude we know that analog audio is important for our project in order to convert it to digital so that in the end we can carry it over HDMI for a single connection. Moreover we will be able to apply these concepts to our device to improve classic video game console output.

### 3.4.1.3 Digital Audio

Digital audio systems are an important aspect of our project in that it deals with the transition of digital equipment from analog environment sources. The achievement of this task requires precise steps in order that the analog signals are converted to digital audio system without disturbances and error. Digital audio systems utilize numbers to represent the original audio waveform as binary data, making the process known as pulse code modulation (PCM). PCM is the form of binary coding used in virtually all digital audio systems. Timing in this process is imperative in order to achieve stability of the audio output. If the instability is not addressed properly prior to this process, timing inaccuracies cannot be removed at a later time and also will result in an unstable stereo imaging and noise issues. So for accuracy the highest audio frequency that a digital system can encode must be less than or equal to  $\frac{1}{2}$  the sampling frequency. The low pass filter is a technology used to record, store, generate and manipulate sound using audio signals encoded in serial digital streaming. For our project we are using the Inter-IC sound chip  $(I^2S)$ . The  $I^2S$  is a serial bus that that will connect the audio decoder to the HDMI receiver and disseminate PCM audio between the integrated circuits. Digital audio is useful in the recording, manipulation, mass production and distribution of sound. There are many benefits when using this system since it does not have the same noise audio problem that analog audio has.

Disturbances in a digital system do not result errors as in analog audio unless the disturbance is so great that the symbol is being misinterpreted as another symbol or disturbance in the sequence of symbols. Also, digital audio can produce a greater frequency of range, which may include but not limited to, compression, storage, processing and transmission components. Whenever you are dealing with corrections in digital audio signals, encoding may be applied for correction measures that might occur in the storage or transmission of the signal. Channel coding refers to a process that is completed when a signal is transmitted and received and it involves designating extra bits and absorbing extra bandwidth to allow for better communication.

### 3.4.1.4 Digital Video

Essentially the process of digitizing video is capturing the analog sine wave at different time span and encapsulating it in a numerical value for each measurement as time great than zero. In order to a more accurate digital reproduction the data has to be captured more often since the sine wave curve is changing continuously as time is progressing. Once data has been digitalized the information is sent in one digital stream that contains both video and audio.

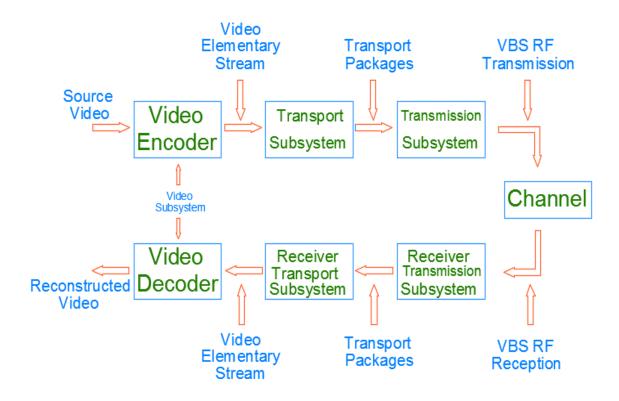

The amount of data on that stream determines the quality of the image, however a stream with high quantity of data requires a larger bandwidth to transmit it. If a data stream has a large amount of details, but the bandwidth is too small the image quality will be poor. The information in the digital stream is in the form of zeroes and ones and it is organized in frames. From this point on, the frames are organized into packets and the packets are organized in segments. The different groups within a digital stream are encoded so that the receiving end can correctly organize it. A digital may contain information from more than one source so it is fundamental that the data from the frames, packets, and segments are sent and received correctly otherwise the digital stream cannot be decoded and the image will be of poor quality. The image drawn shown below gives a detailed visual demonstration as to the process of encoding and decoding an analog signal to digital.

The advantages of having a digital world where most information is shared digitally is that it is easier to manipulate and provides for a much faster editing. With a digital video signal, a person has the capabilities to separate the sound from the image where as in analog form both are congruent and not easily edited. Additionally, with digital video, the image and information is protected and not as susceptible to wear and tear as a video tape cane be. With digital video, the information can be copied multiple times with out losing information or compromising the integrity of the video. With the digital video the data files can be very large and unmanageable without digital video compression.

Figure 9: Encoding and Decoding an Analog Data Signal.

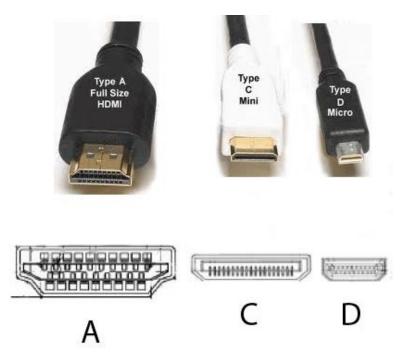

#### 3.4.1.5 HDMI

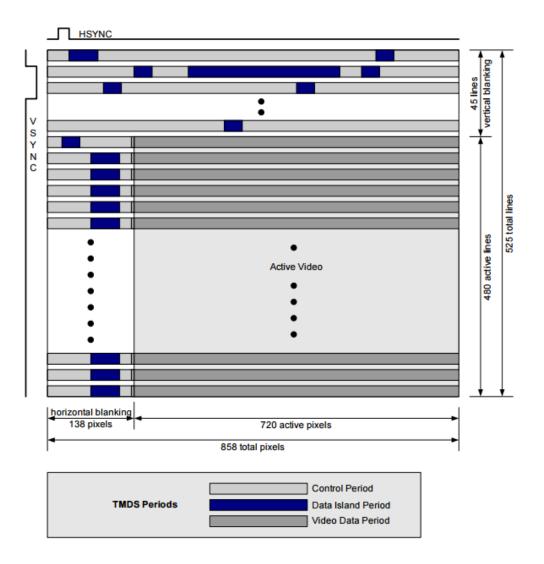

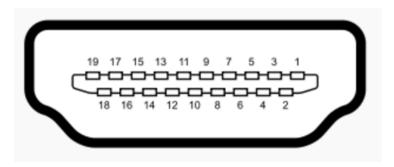

In an effort to provide a low-noise output video signal which is compatible with many displays, we chose to use HDMI as our system's primary output. HDMI uses the EIA/CEA-861 video standard and allows for the transmission of uncompressed audio and video signals using a single cable. An HDMI link can be used for RGB 4:4:4,  $YC_BC_R$  4:4:4, and  $YC_BC_R$  4:2:2 pixel encodings. With a maximum pixel clock of 340MHz, HDMI 1.3 supports resolution up to 2560x1600 using a single digital link. Data is sent in three packet types, control, data island, and video data. The video packet contains pixel information and the data island packet contains audio information as well as auxiliary information. A special encoding scheme is used which reduces the number of transmission line voltage changes by representing an 8-bit packet in an expanded 10-bit form.

A timing diagram for an entire 720x480 pixel video frame is given in Figure 10 below. Video data packets are sent during the active pixel region, this constitutes the color information shown on the display screen. The audio and control packets are sent during the blanking periods before the active regions. A control period is required in between any two periods which are not control periods. Table 4 describes the data transmitted and the encoding type used in each transmission period.

Figure 10: Timing diagram for HDMI video frame. HDMI permission pending.

| Period      | Data<br>Transmitted | Encoding Type                 |  |

|-------------|---------------------|-------------------------------|--|

|             | Transmitted         |                               |  |

| Video Data  | Video Pixels        | Video Data Coding             |  |

|             |                     | (8 bits converted to 10 bits) |  |

| Data Island | Packet Data         | TERC4 Coding                  |  |

|             | -Audio              | (4 bits converted to 10 bits) |  |

|             | Samples             |                               |  |

|             | -InfoFrames         |                               |  |

|             |                     |                               |  |

|             | HSYNC,              |                               |  |

|             | VSYNC               |                               |  |

| Control     | Control             | Control Period Coding         |  |

|             | -Preamble           | (2 bits converted to 10 bits) |  |

|             | -HSYNC,             |                               |  |

|             | VSYNC               |                               |  |

Table 4: Content transmitted during various periods and the encoding type used.

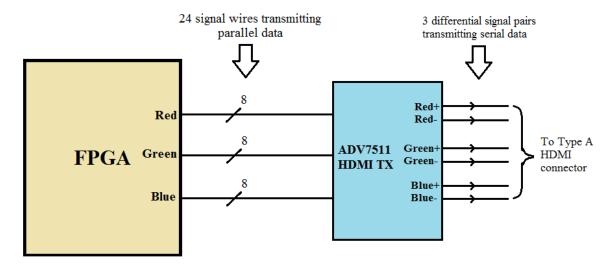

The HDMI standard utilizes a signal format known as transmission minimized differential signaling (TMDS) which helps to reduce noise and improve signal bandwidth. A large benefit of TMDS is the ability to send audio, video, and data in the same stream as packets. The term transmission minimized comes from the encoding scheme used in a TMDS link; the encoding reduces signal transitions from high to low and vice versa by representing 8-bit packets as 10-bits. Differential signals using twisted pair wiring helps to reduce noise due to electromagnetic interference. While an FPGA is capable of performing the 8-bit to 10-bit conversion as well as outputting the required differential signals, for our projects needs it is more practical to use a dedicated HDMI transmitter like the ADV7511. If we were to use the FPGA to create the TMDS HDMI signal it would also require a way for the FPGA to capture the digital audio data from the input audio decoder.

#### 3.4.2 Communications

Arguably the most important aspect of this project not related to direct audiovisual manipulation is the communication amongst all of the discrete device components. As specially designed ICs are available to perform many of the required data transformations and service input/output needs, the primary challenge is then to ensure all of these devices are correctly synchronized and configured relative to one another for their specific task. This is accomplished by the use of one of several serial communications protocols.

For our purposes specifically related to inter-device communication (and thus ignoring insystem reprogramming addressed in section 3.4.5) the relevant protocol options are Inter-Integrated Circuit (I<sup>2</sup>C), Serial Peripheral Interface (SPI), and Universal Asynchronous Receiver/Transmitter (UART). I<sup>2</sup>C is required for use in this project as several of the special purpose ICs are controlled via this protocol. SPI and UART are both presented as potential solutions for inter-device communication for the microcontroller and FPGA. These communications methods are treated in this section.

### 3.4.2.1 I<sup>2</sup>C (Inter-Integrated Circuit)

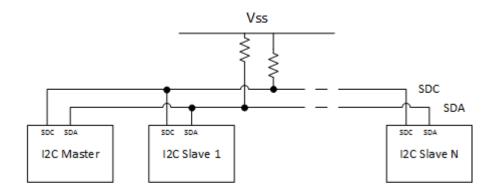

$I^2C$  is a synchronous serial communication protocol intended for use in communications between devices located in relatively close proximity to one another (i.e. for our project on the same PCB).  $I^2C$  requires an extremely small hardware footprint utilizing just two wires for communications, SCL acting as the clock signal and SCA acting as the data wire. Both wires are pulled high and devices manipulate the bus by pulling the specified line low. Multiple devices can exist on the same  $I^2C$  network as each device has its own address specified via 7 or 10 bits. These devices exist as a single Master, responsible for triggering the clock and initiating communications with other devices designated as Slaves. Conventional  $I^2C$  implementations provided for only one master though a multi-master mode does exist where devices are able to change between master and slave as necessary. A diagram of a typical  $I^2C$  network can be seen in Figure 11.

Figure 11: Diagram demonstrating a typical I<sup>2</sup>C network arrangement.

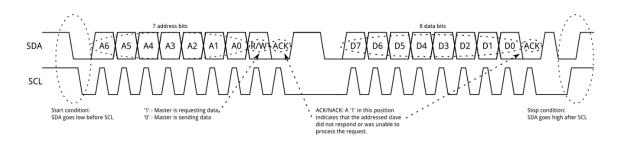

I<sup>2</sup>C data transfer requires use of two separate frames. Address frames specify the device targeted by the master for communications, and data frames carry the data for the requested communication. The address frame also specifies whether the master is requesting to read or write to the addressed slave. Following the address frame, the master or slave (depending on the communication mode selected in the address frame) manipulates the SDA line by leaving it high (logic 1) or pulling the line low (logic 0) to send data 1 bit at a time in 8 bit frames. The SDA line is sampled when SCL is high and changed (if necessary) when SCL is low. The standard specifies that addresses and data are both sent most significant bit first. Each frame ends with a single Ack/NoAck bit. The device that received the previous frame is responsible for pulling SDA low during this bit window to indicate that it successfully received the sent frame. The figure (Figure FIGURE NUMBER) shown below shows a diagram of sample I<sup>2</sup>C communication via an address frame and single data frame including all bits detailed previously. This communication is commonly supported at three speeds defined in modern I<sup>2</sup>C standards, 100 kHZ (100 kbps), 400 kHZ (400 kbps "fast mode") and 1 MHz (1 Mbps "fast mode plus").

Figure 12: I<sup>2</sup>C example address and data frame clock diagram. Courtesy of Sparkfun.

$I^2C$  is supported by a large number of ICs requiring advanced configuration or serial communications, and supported specifically by the various decoder, encoder, and transmitters required in our project. Additionally, there are readily available  $I^2C$  implementations for FPGAs via OpenCores and support for  $I^2C$  at the hardware and software level in all considered microcontrollers.

## 3.4.2.2 Serial Peripheral Interface (SPI)

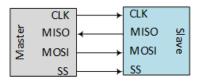

While I<sup>2</sup>C will be used extensively in this project due to requirements for specific devices like the audio/video encoders, decoders, and transmitter/receivers, it is but one option for implementation of the microcontroller and FPGA communications interface. Another option, presented here, is Serial Peripheral Interface, commonly referred to as SPI. SPI shares many functional characteristics with I<sup>2</sup>C. Both protocols are synchronous utilizing a clock signal to determine when to send, read, and receive data. Both also have this clock signal controlled by a single device designated as Master and support multiple devices configured as Slave.

There are two key differences between the protocols. One is that under SPI, the Slave currently selected for communications with the Master is selected by a separate signal line called Slave Select (SS). For our implementation there would be at most 2 SPI devices (the microcontroller and the FPGA SPI interface) so this is essentially an enable wire as opposed to  $I^2C$ 's initiation via address frames. The second is that SPI supports full duplex communications so that Master and Slave can both send and receive data simultaneously if configuration permits. This is accomplished by using two separate data wires, Master Out Slave In (MOSI) and Master In Slave Out (MISO). The wire names accurately describe their use as each being responsible for communication in one direction. Figure 13 below shows the control path for all wires in an expected implementation within this project featuring a single master and single slave.

Figure 13: SPI control signal flow and connections expected in a simple implementation.

These additional connections are a key differentiator between SPI and both  $I^2C$  and UART communications. Where both  $I^2C$  and UART are implemented using only two wires, SPI requires 4 to support its greater feature set. At the implementation level, SPI is also made more complicated in that it is not a true communications standard. Communication rates and data formatting (frames, packets, etc) are all left to the end user to define their implementation. While this loose definition does provide flexibility, the additional work required to define a complete communications interface without even such building blocks as agreed upon frame sizes is potentially considerable.

While the standard itself is not particularly clearly defined, SPI support is implemented in most microcontrollers in the class needed for this project. Microcontroller vendors typically also provide libraries or reference designs utilizing and implementing the SPI bus. Also, SPI functional interface blocks are readily available for FPGAs via OpenCores.

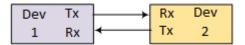

#### 3.4.2.3 UART (Universal Asynch. Receiver/Transmitter)

Universal Asynchronous Receiver/Transmitter communications, or UART, is conceptually the simplest of the protocols reviewed for this project. Like  $I^2C$  it uses only two wires for communication, but as the communication itself is asynchronous there is no clock wire. One wire is designated as the device's transmit (Tx) wire, and the other is the receive (Rx) wire. Each device then has its Tx terminal connected to the other device's Rx terminal and its Rx terminal connected to the other device's Tx terminal. A simple drawing in Figure 14 below shows this connection as expected between two devices.

Figure 14: Two device UART connection.

Since UART does not use a clock wire, it requires explicit configuration prior to use concerning clock rates and frame formats. The data rate, number of start bits, number of data bits, number of stop bits, and parity format, and data endianness are all required to be known prior to correct communication. UART is supported by virtually all devices capable of serial communications whether as pure asynchronous serial or via a standard like RS232 or TTL. However, it boasts lower maximum throughput values than the other options, with data rates of around 115 kbps being a typical maximum before errors due to lack of throughput capabilities occur. Nonetheless, it poses an attractive alternative to the synchronous protocols if data throughput requirements between the microcontroller and FPGA can be kept low.

### 3.4.3 FPGA

A field programmable gate array (FPGA) will be used as the computational core of our system. Due to real-time constraints a microprocessor would be ill-suited for the required image-processing. The inherent parallelism of the FPGA device makes it well suited for real-time processing of a digital video stream. The HDL language of choice for this project is Verilog because of the language's low-level structure making it ideal for fine-grain image processing operations. The task of the FPGA in this system is to scale the resolution of each image frame in an input video stream by a positive scalar value. Multiple parallel data paths will be implemented to provide different processing modes, therefore a high-capacity FPGA is desired. In this section we discuss the various device families under consideration and the development environment chosen for this project.

### 3.4.3.1 Xilinx Spartan-3 Family

The first family of devices under consideration is Xilinx's Spartan-3 FPGA family. The Spartan-3 family is based on a 4-input LUT logic cell structure with capacities ranging from 1,728 logic cells for the low-end XC3S250 to 74,880 logic cells for the flagship XC3S5000 FPGA. Each FPGA in this family features hardware multipliers and digital clock management (DCM) blocks. The dedicated multipliers are a necessity for operations such as convolution which is frequently used in image processing. The digital clock management is needed to synchronized FPGA logic cells to external video clock signals, these DCM blocks help reduce clock skew and jitter.

The specific device in the Spartan-3 family under consideration is the XC3S400. At a cost of \$33.75 per unit the XC3S400 comes equipped with 8,064 logic cells and 294kb block memory. The package type is a 256-LBGA with 173 available user I/O pins, 3.3V logic I/O is supported. The supply voltage is 1.14V-1.26V with a max operating temperature of 85°C. We would have preferred to use the XC3S1500 for its high logic capacity but due to low availability it was abandoned as a choice. The block RAM is arranged in 18kb blocks of dual-port RAM, dual-port RAM is useful to use as a frame buffer due to the ability to perform a read and write operation in the same clock cycle. There are 16 dedicated multipliers available, each is able to support two 18-bit operands. The XC3S400 comes equipped with 4 digital clock management blocks which will be needed to synchronize internal logic resources to external clock signals.

From a cost and availability perspective, the XC3S400 is a good choice. The device supports a sufficient number of I/O and has decent logic capacity. While the available memory is quite large, 294kb would may be inadequate for higher resolution frame buffers. A possible solution would be to utilize spare logic cells as distributed memory, however this should only be done as a last resort. The number of DCM blocks is also a cause for concern due to the number of external clocks that the FPGA will potentially have to synchronize with. The FPGA will need to synchronize with the video decoder's pixel clock, horizontal clock, and vertical clock in addition to the clock used for communication between FPGA and MCU.

### 3.4.3.2 Xilinx Spartan-6 Family

The second family of devices under consideration is Xilinx's Spartan-6 FPGA family. The Spartan-3 family is based on an improved 6-input LUT logic cell structure with capacities ranging from 3,840 logic cells for the low-end XC6SLX4 to 147,443 logic cells for the flagship XC6SLX150T FPGA. Each FPGA in this family features hardware multipliers and clock management tiles (CMT).

The specific device in the Spartan-6 family under consideration is the XC6SLX9. At a cost of \$21.84 per unit the XC6SLX9 comes equipped with 9,152 logic cells and 589kb block memory, providing a much better price to capacity ratio than that of the XC3S400. The package type is a 324-LFBGA with 200 available user I/O pins, 3.3V logic I/O is supported. The supply voltage is 1.14V-1.26V with a max operating temperature of 85°C. Like the Spartan-3 family, the block RAM is arranged in 18kb blocks of dual-port RAM. New to the Spartan-6 family is the ability to treat each 18kb block as two independent 9kb blocks. The Spartan-6 family utilizes DSP48A1 slices which each contain an 18x18 multiplier, an adder, and an accumulator. The XC6SLX9 contains 16 DSP48A1 slices. The clock management tiles (CMT) expand upon the DCM concept with each tile containing two DCMs and one phase-locked loop (PLL). The XC6SLX9 contains two CMTs which puts it at four DCMs and two PLLs.

From a cost perspective, the XC6SLX9 is a better option than the XC3S400. The XC6SLX9 logic cells are much denser due to utilizing a 6-input LUT plus 4 D-flip-flop cell structure versus the XC3S400's 4-input LUT plus one d-flip-flop cell structure. While the available memory is quite large and almost double of that available in the XC3S400, 589kb would still be inadequate for higher resolution frame buffers. The XC6SLX9 has the same number of DCMs as the XC3S400, however it contains two extra PLLs will be useful in our design.

## 3.4.3.3 Xilinx Artix-7 Family

The final family of devices under consideration is Xilinx's Artix-7 FPGA family. The Artix-7 family is based on a 6-input LUT logic cell structure with capacities ranging from 16,640 logic cells for the low-end XC7A15T to 215,360 logic cells for the flagship XC7A200T FPGA. Each FPGA in this family features DSP48E1 slices and clock management tiles. Each DSP48E1 slice has a pre-adder, a 25x18 multiplier, an adder, and an accumulator. Each clock management tile has one mixed-mode clock manager (MMCM) and on phase-locked loop (PLL).

The specific device in the Artix-7 family under consideration is the XC7A35T. At a cost of \$39.55 per unit the XC7A35T comes equipped with 33,280 logic cells, 1800kb block memory, and an additional 400kb of distributed memory. The package type is a 256-LBGA with 170 available user I/O pins, 3.3V logic I/O is supported. The supply voltage is 0.95V-1.05V with a max operating temperature of 100°C. The block RAM is arranged in 36kb

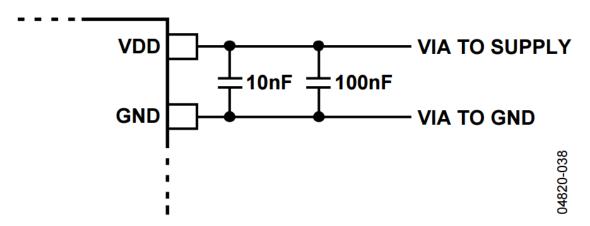

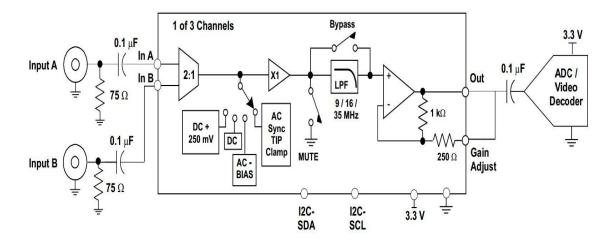

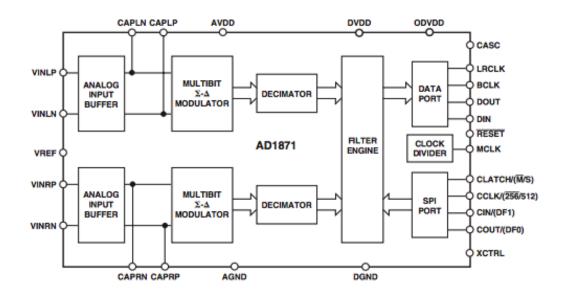

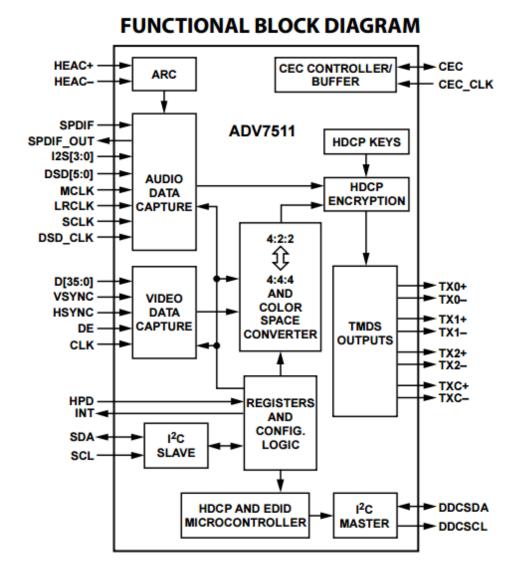

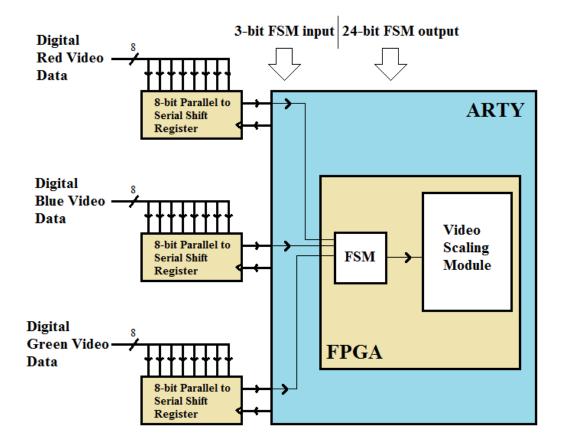

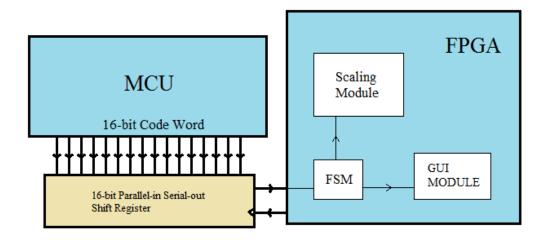

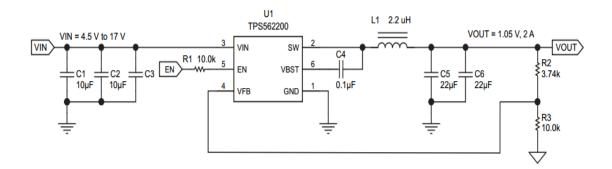

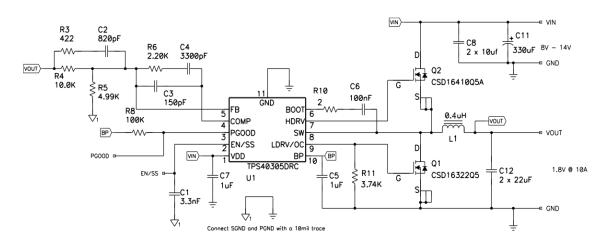

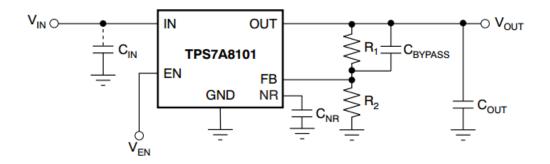

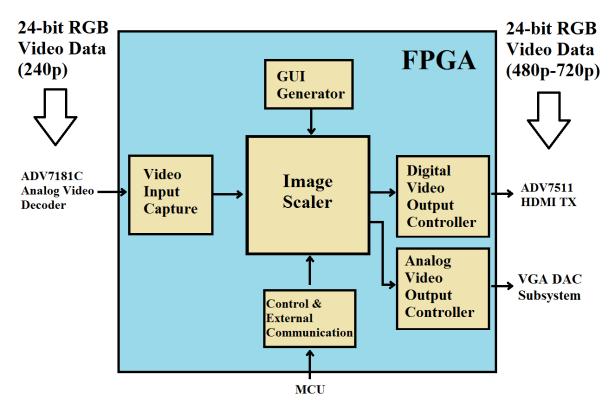

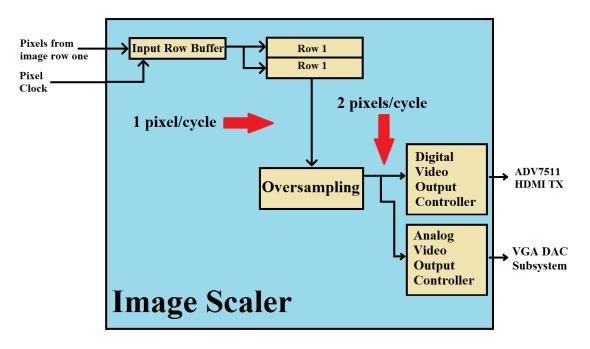

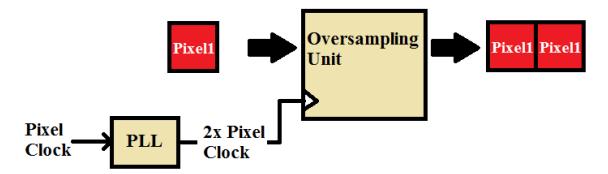

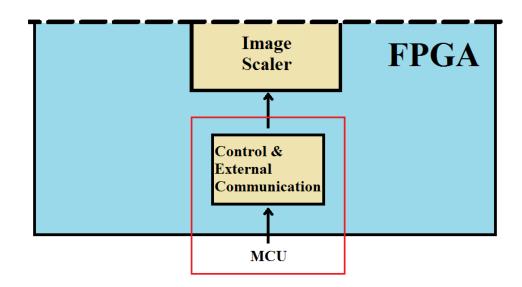

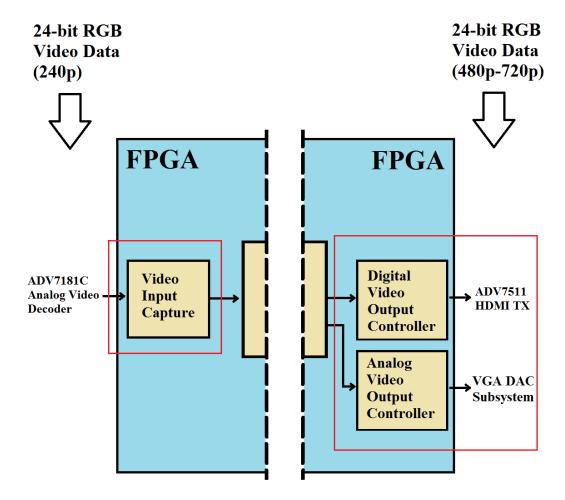

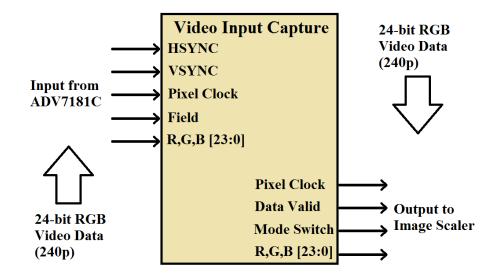

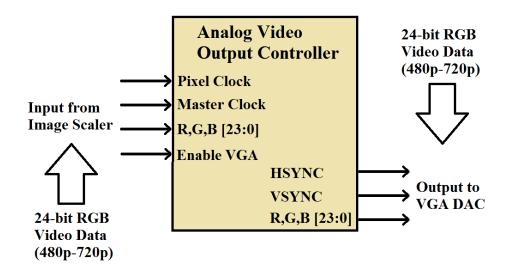

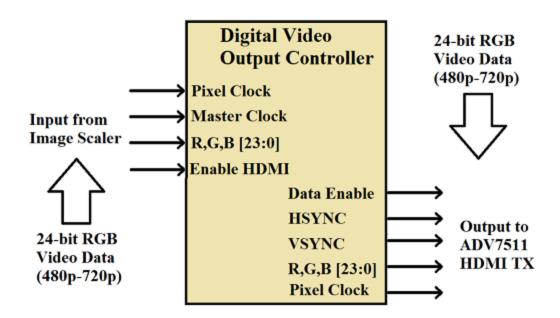

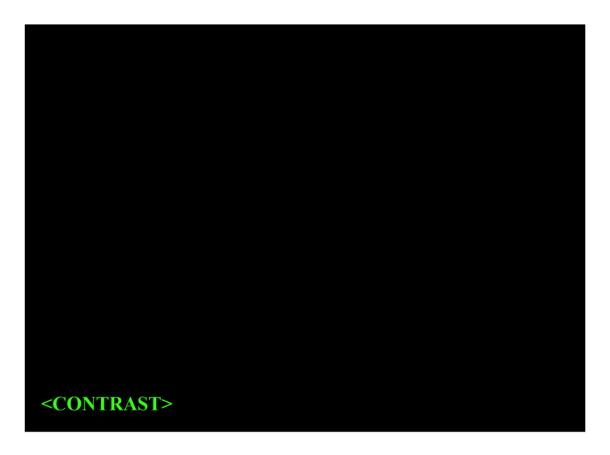

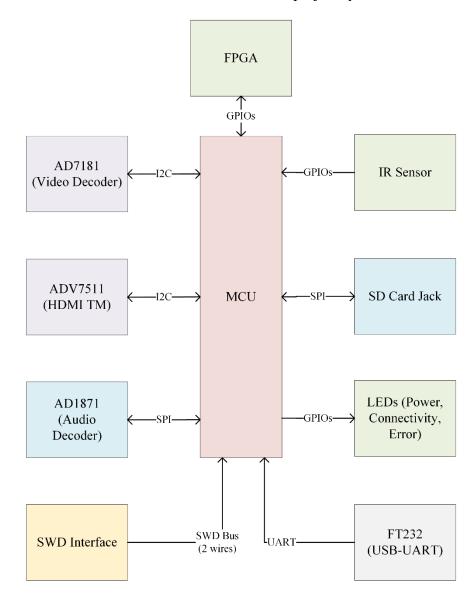

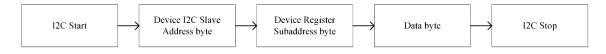

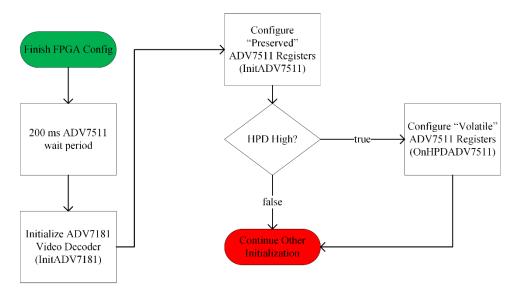

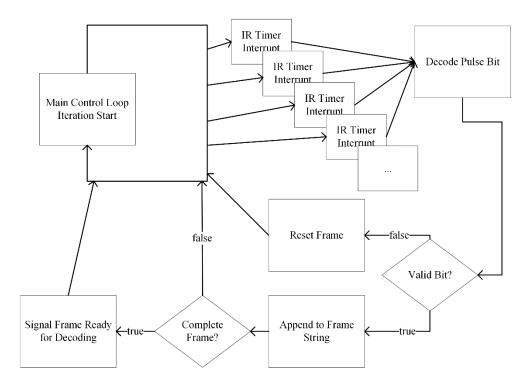

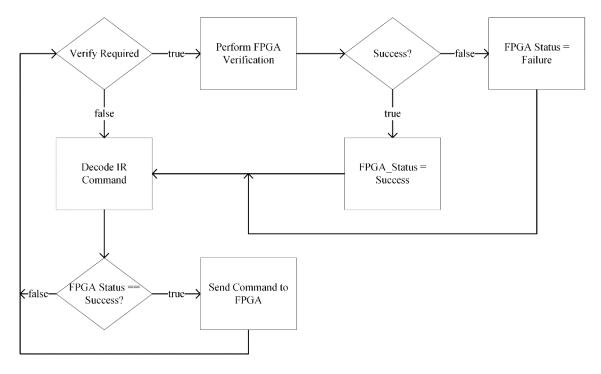

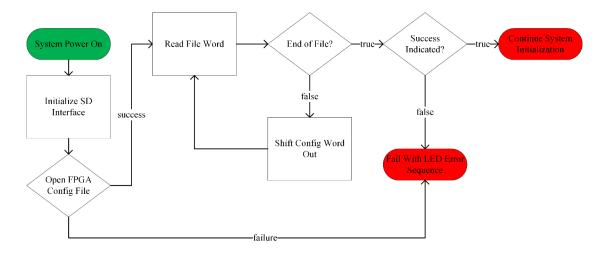

blocks of dual-port RAM, dual-port RAM is useful to use as a frame buffer due to the ability to perform a read and write operation in the same clock cycle. There are 90 DSP48E1 slices available, each of which is essentially a multiply accumulate unit. The XC7A35T comes equipped with 5 clock management tiles which will be needed to synchronize internal logic resources to external clock signals.